L'atelier PSG/SCC FPGA

Reprise du message précédent

je pense qu'il est plus facile de construire tout le MSX genre one chip que de s'en servir comme périphériqueles 5V tolérants ne doivent pas être vraiment avec les niveaux de tension requis des portes classiques

il faut potasser les datasheets en anglais pour bien comprendre les subtilités

Comme plus je bricolais et moins ça marchait j'ai tout recommencé.

Tout est rentré dans l'ordre niveau SCC, reste encore la SRAM à câbler

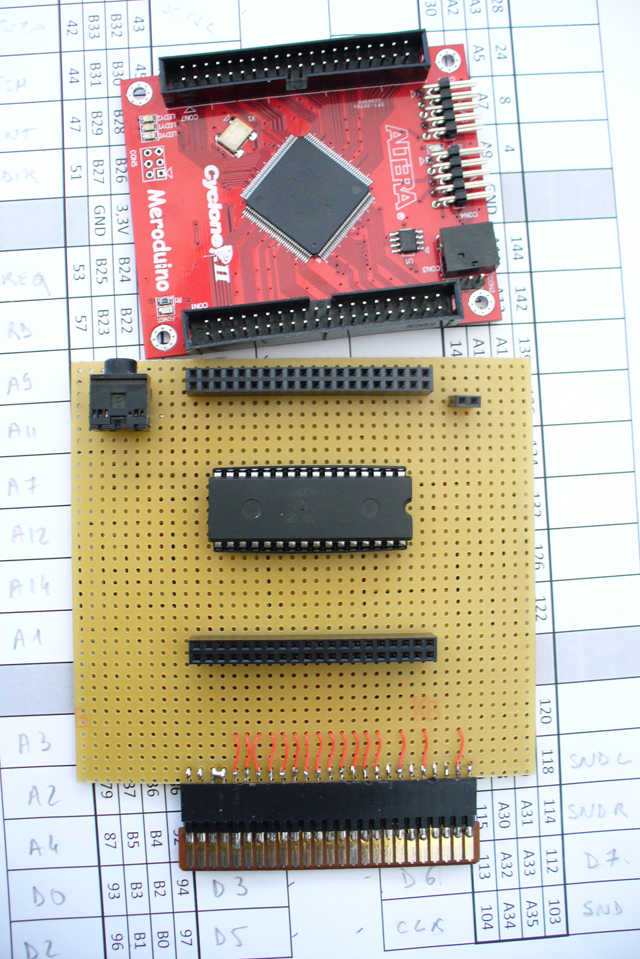

Voila une photo de la bête

La carte sans le Cyclone

Comme je reprends de zéro, j'aimerais bien tester une version avec RAM.

Par contre je comprends rien au VHDL et le texte est pas clair donc je sais pas si c'est un mapper RAM ou de la RAM SCC+

A votre avis :

----------------------------------------------------------------

-- Title : psgsccr.vhd

-- Function : PSG + SCC + RAM(EseSCC/SNATCHER compatible)

-- Date : 28th,August,2000

-- Revision : 1.01

-- Author : Kazuhiro TSUJIKAWA (ESE Artists' factory)

----------------------------------------------------------------

Tout est rentré dans l'ordre niveau SCC, reste encore la SRAM à câbler

Voila une photo de la bête

La carte sans le Cyclone

Comme je reprends de zéro, j'aimerais bien tester une version avec RAM.

Par contre je comprends rien au VHDL et le texte est pas clair donc je sais pas si c'est un mapper RAM ou de la RAM SCC+

A votre avis :

----------------------------------------------------------------

-- Title : psgsccr.vhd

-- Function : PSG + SCC + RAM(EseSCC/SNATCHER compatible)

-- Date : 28th,August,2000

-- Revision : 1.01

-- Author : Kazuhiro TSUJIKAWA (ESE Artists' factory)

----------------------------------------------------------------

il y a un mapper SCC vu les adresses

-- Mapped I/O port access on 5000-57FFh ... Bank resister write

-- Mapped I/O port access on 7000-77FFh ... Bank resister write

-- Mapped I/O port access on 9000-97FFh ... Bank resister write

-- Mapped I/O port access on B000-B7FFh ... Bank resister write

mais il y a aussi du code pour une interface SCSI

-- SCSI controller access enable (4000-5FFFh/A000-BFFFh)

le probléme c'est qu'il n'y a pas de schéma avec le code

-- Mapped I/O port access on 5000-57FFh ... Bank resister write

-- Mapped I/O port access on 7000-77FFh ... Bank resister write

-- Mapped I/O port access on 9000-97FFh ... Bank resister write

-- Mapped I/O port access on B000-B7FFh ... Bank resister write

mais il y a aussi du code pour une interface SCSI

-- SCSI controller access enable (4000-5FFFh/A000-BFFFh)

le probléme c'est qu'il n'y a pas de schéma avec le code

Résultats des tests d'hier soir.

J'ai branché une SRAM 512ko.

J'ai du supprimer une des 2 rams gérées par le fichier à cause d'un manque de pins sur mon Cyclone.

TESTRAM ne trouve pas de MAPPER

SCROM et ROMLOAD ne trouve pas de sound cartridge

La BASS DEMO elle détecte bien une SCC

EXECROM détecte une SCC+ en slot 1 mais pas de megaram

MGLOAD me renvoie un improper cartridge

Il y a peut être un autre programme à tester, moi je n'en connait pas d'autre

J'ai branché une SRAM 512ko.

J'ai du supprimer une des 2 rams gérées par le fichier à cause d'un manque de pins sur mon Cyclone.

TESTRAM ne trouve pas de MAPPER

SCROM et ROMLOAD ne trouve pas de sound cartridge

La BASS DEMO elle détecte bien une SCC

EXECROM détecte une SCC+ en slot 1 mais pas de megaram

MGLOAD me renvoie un improper cartridge

Il y a peut être un autre programme à tester, moi je n'en connait pas d'autre

Ca avance

SCROM et ROMLOAD reconnaissent la bête mais c'est pas gagné

SCROM et ROMLOAD reconnaissent la bête mais c'est pas gagné

j'ai regardé pour dll le soft il est plutôt énorme j'imagines que c'est parce qu’il y a déjà une base de donnée de composants "classiques installé apres il faut que je regardes si je comprends comment tout le bins fonctionne car pour le moment je ne comprends pas grand chose a ce que je lis concernant la programmation de la puce -_-.

Je te rassure Galine, je n'ai rien compris non plus

Mon Github ->[/b] github.com/msxlegend

challenge 2013 -> neodream MSX 2013

Concepteur du -> KCX Bluetooth transmitter

Demo Terminator2 T2.zip

avec ça on est pas dans le c...  . enfin il y a des trucs qui fonctionnent très bien de ce que j'ai pus lire comme l'ide beer l’émulation scc et psg je crois qu'il ne faut pas être trop gourmand et y aller progressivement allez commençons par une extension turbo-r +

. enfin il y a des trucs qui fonctionnent très bien de ce que j'ai pus lire comme l'ide beer l’émulation scc et psg je crois qu'il ne faut pas être trop gourmand et y aller progressivement allez commençons par une extension turbo-r +

. enfin il y a des trucs qui fonctionnent très bien de ce que j'ai pus lire comme l'ide beer l’émulation scc et psg je crois qu'il ne faut pas être trop gourmand et y aller progressivement allez commençons par une extension turbo-r +

. enfin il y a des trucs qui fonctionnent très bien de ce que j'ai pus lire comme l'ide beer l’émulation scc et psg je crois qu'il ne faut pas être trop gourmand et y aller progressivement allez commençons par une extension turbo-r +

Ce soir je blinde toutes les sorties de buffers.

Je croise les doigts

Jipe, il y a aussi un paramètre pour régler l'impédance des sorties, ça te dis quelque chose ?

Je croise les doigts

Jipe, il y a aussi un paramètre pour régler l'impédance des sorties, ça te dis quelque chose ?

Je crois qu'il n'y a malheureusement pas de secrets ce genre de puces implique de tout reprendre de zéro et du coup de faire des montages de plus en plus complexes pour en comprendre le fonctionnement finalement nous sommes trop pressé de pouvoir utiliser les propriétés de ces puces sur nos bon vieux msx ce qui fait que ça ne fonctionne pas forcément...

Je demandais par rapport à l'impédance si tu connaissais ce phénomène en électronique classique.

Merci pour cet éclaircissement, petite lueur dans l’obscurité

Pour les puces FPGA, on retrouve effectivement la notion d'impédance qui affecte vraisemblablement la vitesse, la consommation et p'tet le bruit de fond. Mais là, c'est beaucoup trop compliqué pour moi.

Par contre, pour la programmation des FPGA la notion de tri-state (appelé Hi-Z pour "high impedance" est commune lors de l'utilisation, notamment bidirectionnelle, des pins. http://fr.wikipedia.org/wiki/Haute_imp%C3%A9dance

Je te cherche un exemple en rentrant du taf.

Par contre, pour la programmation des FPGA la notion de tri-state (appelé Hi-Z pour "high impedance" est commune lors de l'utilisation, notamment bidirectionnelle, des pins. http://fr.wikipedia.org/wiki/Haute_imp%C3%A9dance

Je te cherche un exemple en rentrant du taf.

Philips.NMS.8245/50/80, Sony.F1XV/HBF-700D, Pana.FSA1FX/A1WX(x2)/A1GT, OCM, GR8BIT.... et ...

Répondre

Vous n'êtes pas autorisé à écrire dans cette catégorie