L'atelier PSG/SCC FPGA

Reprise du message précédent

A tester aussi

Je me demandais s'il n'y aurais pas un problème de SRAM trop lente ou trop rapide

trop rapide, pas grave... trop lente j'en doute si ton FPGA cadence son bus comme un vrai Z80 @ 3.58MHz tu peux avoir de la mémoire à 200ns sans que cela pose problème, je crois même que 250ns ça passe encore

TurboR GT (1Mo), CANON V20! ( en kit, modif 2+ en cours)

Pas encore retrouvés: V9990, Grafx9000, SUNRISE IDE 2x CF, SUNRISE MOONSOUND, FM PAC, MUSIC MODULE, NMS8280, SD SNATCHER,...

You've got MP ... feel free to share

J'espere que les corrections ,et le clock divider vont te permettre de mettre le dossier en resolut apres avoir partage le bordel que tu a recus en MP

J'espere que les corrections ,et le clock divider vont te permettre de mettre le dossier en resolut apres avoir partage le bordel que tu a recus en MP

HB-F700F(X2),A1GT,Altera DE1 + slots , Sunrise IDE CF,FMPAC, Music Module,Slot expander 8X (X3) ,PlaySoniq, et autres

Désolé je ne peux rien faire avec ces fichiers à cause des ports utilisés

Oui

J'ai synchronisé /CE de la SRAM avec inv(/WR) du BUS et ça marche.

Je sais pas trop pourquoi mais les résultats sont là.

Par contre ça ne marche pas sur MSX1 ni sur TurboR alors que ça roule sur MSX2 et MSX2+

J'ai synchronisé /CE de la SRAM avec inv(/WR) du BUS et ça marche.

Je sais pas trop pourquoi mais les résultats sont là.

Par contre ça ne marche pas sur MSX1 ni sur TurboR alors que ça roule sur MSX2 et MSX2+

Je confirme que la partie SCC en VHDL de Kazuhiro TSUJIKAWA fonctionne.

http://www.hat.hi-ho.ne.jp/tujikawa/esepld/scc.zip

Testé sur :

HB75F

NMS8245

FSA1 ST

Je vais essayer de pousser plus loin

J'ouvrirais un autre topic, celui ci ne ressemble plus à rien. Edité par Fabf Le 27/02/2015 à 20h52

http://www.hat.hi-ho.ne.jp/tujikawa/esepld/scc.zip

Testé sur :

HB75F

NMS8245

FSA1 ST

Je vais essayer de pousser plus loin

J'ouvrirais un autre topic, celui ci ne ressemble plus à rien. Edité par Fabf Le 27/02/2015 à 20h52

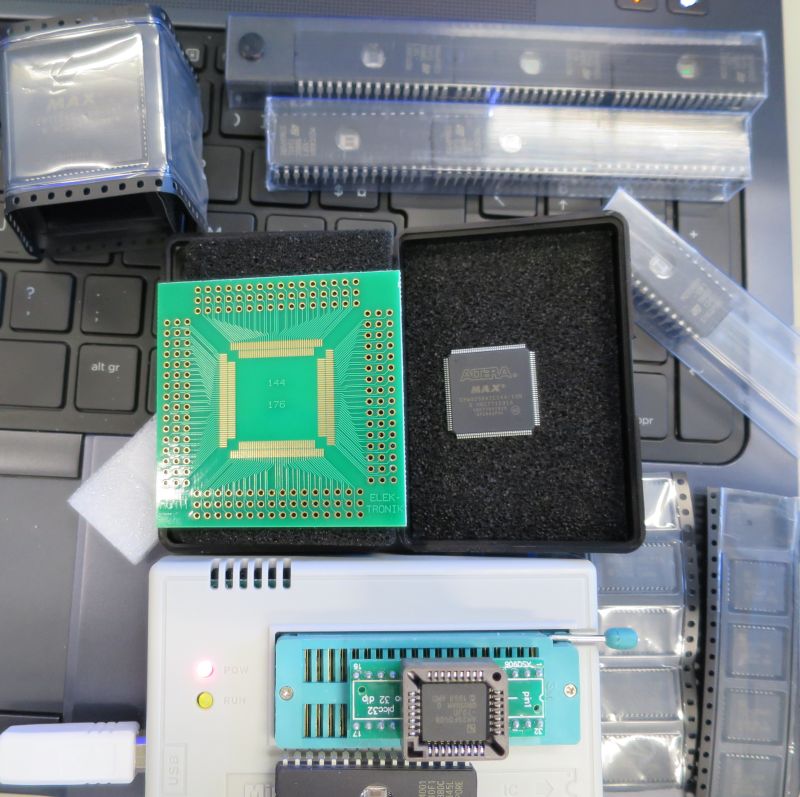

La carte préparée dans les règles avec les résistances qui changent tout

En bleu la carte de dev FPGA.

Le tout assemblé, prêt à hurler des sons SCC

Top-level Entity Namescc

FamilyCyclone II

DeviceEP2C5T144C8

Timing ModelsFinal

Total logic elements708 / 4,608 ( 15 % )

Total combinational functions645 / 4,608 ( 14 % )

Dedicated logic registers239 / 4,608 ( 5 % )

Total registers239

Total pins32 / 89 ( 36 % )

Total virtual pins0

Total memory bits2,048 / 119,808 ( 2 % )

Embedded Multiplier 9-bit elements0 / 26 ( 0 % )

Total PLLs0 / 2 ( 0 % )

En bleu la carte de dev FPGA.

Le tout assemblé, prêt à hurler des sons SCC

Top-level Entity Namescc

FamilyCyclone II

DeviceEP2C5T144C8

Timing ModelsFinal

Total logic elements708 / 4,608 ( 15 % )

Total combinational functions645 / 4,608 ( 14 % )

Dedicated logic registers239 / 4,608 ( 5 % )

Total registers239

Total pins32 / 89 ( 36 % )

Total virtual pins0

Total memory bits2,048 / 119,808 ( 2 % )

Embedded Multiplier 9-bit elements0 / 26 ( 0 % )

Total PLLs0 / 2 ( 0 % )

Bonsoir,

je comprend mieux maintenant le probléme de résistance

Ils auraient du étudier un sytéme pour le JTAG avec un connecteur coudé. A chaque fois, tu es obligé d'enlever la carte pour brancher ton USB Blaster.

Mais tu as eu une bonne idée de faire une encoche sur le circuit

je comprend mieux maintenant le probléme de résistance

Ils auraient du étudier un sytéme pour le JTAG avec un connecteur coudé. A chaque fois, tu es obligé d'enlever la carte pour brancher ton USB Blaster.

Mais tu as eu une bonne idée de faire une encoche sur le circuit

Oui je comprends mieux aussi maintenant.

La tension 5V en direct ne grille pas forcement les entrées du FPGA mais les "overdrive" ce qui rend les valeurs aléatoires ou/et irrégulières.

Je trouve qu'il y a une différence au niveau du son qui est plus doux et il n'y a plus de plop au démarrage.

La tension 5V en direct ne grille pas forcement les entrées du FPGA mais les "overdrive" ce qui rend les valeurs aléatoires ou/et irrégulières.

Je trouve qu'il y a une différence au niveau du son qui est plus doux et il n'y a plus de plop au démarrage.

Je n'utilise plus le PSG dans cette dernière version.

En effet ce serait dommage de n'utiliser que 15% de l'engin

En effet ce serait dommage de n'utiliser que 15% de l'engin

Fabf :

Je trouve qu'il y a une différence au niveau du son qui est plus doux et il n'y a plus de plop au démarrage.

Ça fait comme sur émulateur apparemment. La puce SCC réel fait comme la puce SN76489. Si on ne baisse pas le volume dès qu'on l'active, il se produit un son parasite car les registres contiennent n'importe quoi à l'allumage. La puce SN76489, c'est pire car elle n'a rien pour l'activer. Elle est activée dès qu'elle est alimentée. Edité par GDX Le 01/03/2015 à 11h20

Fabf :

La carte préparée dans les règles avec les résistances qui changent tout

En bleu la carte de dev FPGA.

En bleu la carte de dev FPGA.

J'ai commandé la même!

le grands esprits se rencontrent, il parait

le grands esprits se rencontrent, il parait

Pas encore reçu à cause du nouvel an chinois

sinon j'ai reçu les autres choses

il faut que je me dégage un peut de temps, mais je vais pouvoir commencer les choses sérieuses.

J'ai même quelques TXB108 qui vont bien pour la passerelle 5v/3.3v.

TurboR GT (1Mo), CANON V20! ( en kit, modif 2+ en cours)

Pas encore retrouvés: V9990, Grafx9000, SUNRISE IDE 2x CF, SUNRISE MOONSOUND, FM PAC, MUSIC MODULE, NMS8280, SD SNATCHER,...

Répondre

Vous n'êtes pas autorisé à écrire dans cette catégorie