L'atelier [EN COURS] Méga S-Ram SCC => 1024 => Wave SCSI Convertion d'une mégaSramSCC en Wave SCSI

il existe 3 types de Cartouches SCC.

A, B et C.

Le principe de base pour modifier une SCC en FlashRam étant identique au FlashRom, (4 ou 5 fils fils relient la SCC à L'Eeprom comme à la S-ram) il y a fort à parier que seules les Cartouches de Type A et B soient compatibles!

Nb: Jipe saura certainement dire si le Type C est impossible ou alors si personne ne s est penché dessus pour trouver la bonne implantation.

Voici le lien pour voir les Types A, B et C des SCC http://www.msxvillage.fr/articles/articles.php?id=51&cat=2

Tout cela reste à confirmer, mais je pense pas me tromper Edité par

igal

Le 21/05/2012 à 09h10

Edité par

igal

Le 21/05/2012 à 09h10

A, B et C.

Le principe de base pour modifier une SCC en FlashRam étant identique au FlashRom, (4 ou 5 fils fils relient la SCC à L'Eeprom comme à la S-ram) il y a fort à parier que seules les Cartouches de Type A et B soient compatibles!

Nb: Jipe saura certainement dire si le Type C est impossible ou alors si personne ne s est penché dessus pour trouver la bonne implantation.

Voici le lien pour voir les Types A, B et C des SCC http://www.msxvillage.fr/articles/articles.php?id=51&cat=2

Tout cela reste à confirmer, mais je pense pas me tromper

Edité par

igal

Le 21/05/2012 à 09h10

Edité par

igal

Le 21/05/2012 à 09h10

Jipe :

merci , le MA19 ça laisse supposer qu'une taille mémoire supérieure a 512k est possible avec ce montage d'ou les 2 /CS0 et /CS1 présents

en théorie cela veux dire que la Wave-SCSI peut avoir 1024k de Sram embarquée.

En mapper 8k celui qui nous intéresse puisqu'il est aussi dans la cartouche SCC la correspondance est la suivante :

B0 MA13

B1 MA14

B2 MA15

B3 MA16

B4 MA17

B5 MA18

B6 MA19

B7 MA20

le mapper SCC s'arrête a MA18 donc B5

les signaux B6 et B7 sont donc construits par les puces du circuit

en théorie cela veux dire que la Wave-SCSI peut avoir 1024k de Sram embarquée.

En mapper 8k celui qui nous intéresse puisqu'il est aussi dans la cartouche SCC la correspondance est la suivante :

B0 MA13

B1 MA14

B2 MA15

B3 MA16

B4 MA17

B5 MA18

B6 MA19

B7 MA20

le mapper SCC s'arrête a MA18 donc B5

les signaux B6 et B7 sont donc construits par les puces du circuit

Au dessus Jipe nous donne la correspondance des appellations entre les mapper ASCII8 et Konami 8.

Jipe :

1024k = 512k x2

donc lire

512k X 2 => il faut juste cabler le MA17 sur la mémoire et remplacer le signal MA17 par MA18 pour génerer les CS0 CS1 sur le 3 du HC139 (Source Jipe)

1024k = 512k x2

donc lire

512k X 2 => il faut juste cabler le MA17 sur la mémoire et remplacer le signal MA17 par MA18 pour génerer les CS0 CS1 sur le 3 du HC139 (Source Jipe)

La manipulation nécessaire pour gérer 2 X 512 au lieu de 512 seulement.

Dans un premier temps, je vais donc essayé d'appliquer ces informations sur le dessin ci dessous sans s'occuper de la partie SCSI mais juste SRAM 512 X 2

Edité par

igal

Le 26/05/2013 à 15h22

Edité par

igal

Le 26/05/2013 à 15h22

Jipe :

merci , le MA19 ça laisse supposer qu'une taille mémoire supérieure a 512k est possible avec ce montage d'ou les 2 /CS0 et /CS1 présents

en théorie cela veux dire que la Wave-SCSI peut avoir 1024k de Sram embarquée.

en théorie cela veux dire que la Wave-SCSI peut avoir 1024k de Sram embarquée.

La description du mapper SCC dit ceci :

Citation :

Mapper Konami5 = Megarom SCC/SCC+ avec pages de 8Ko

Adresses de changement de page :

Format de la valeur pour les megarom SCC :

Format de la valeur pour les megarom SCC+ :

Adresses de changement de page :

- Bank 1 (4000h ~ 5FFFh) : 5000h ~ 57FFh (seule 5000h est utilisée dans les jeux) (page 00h activée à l'initialisation)

- Bank 2 (6000h ~ 7FFFh) : 7000h ~ 77FFh (seule 7000h est utilisée dans les jeux) (page 01h activée à l'initialisation)

- Bank 3 (8000h ~ 9FFFh) : 9000h ~ 97FFh (seule 9000h est utilisée dans les jeux) (page 02h activée à l'initialisation)

- Bank 4 (A000h ~ BFFFh) : B000h ~ B7FFh (seule B000h est utilisée dans les jeux) (page 03h activée à l'initialisation)

Format de la valeur pour les megarom SCC :

- Bits 0~5 = Numéro de page. Si tous à 1 dans le Bank 3, l'accès aux registres de l'SCC devient possible.

- Bits 6~7 = Inutilisés

Format de la valeur pour les megarom SCC+ :

- Bits 0~5 = Numéro de page. Si tous à 1 dans le Bank 3 (et bit 7 à 0), l'accès aux registres de l'SCC devient possible.

- Bit 6 = Inutilisé

- Bit 7 = Si à 1, le Bank 4 permettra d'accéder aux registres de l'SCC+ (actif seulement en mode ROM). Inutilisé dans les banks 1 ~ 3.

2 bits sont inutilisés donc il reste 6 bits pour gérer le mapper. Ce qui fait : 6 x 8ko = 512Ko maximum.

L'SCC de Type C a les broches 1, 3 et 17 de sa ROM reliées au +5V. C'est ça qui doit gêner pour y mettre une flash-rom mais je ne pense pas que ça gêne si l'on y met une SRAM. Edité par GDX Le 28/05/2013 à 12h59

Salut Gdx.

En l'état, effectivement, une SCC se limite à 512Ko de mapper.

Mais avec le Trio LS74(modifié) + LS08(ajouté) + LS139(ajouté), on doit arriver à "Basculer" d'une Mémoire à une autre.

Le problème est de savoir comment le faire.

Par exemple, je viens tout juste de Monter une SRAM en gigogne tous les signaux en parallèles sauf [WE SRAM Pin 29] et [CS SCRAM Pin22] qui doivent recevoir respectivement [MA18 SCC Pin40] et [MA17 SCC Pin39].

Le problème est que puisque les 2 SRAM sont branchées en parallèles, [MA18 SCC Pin40] et [MA17 SCC Pin39] sont déjà connectés respectivement sur [A18 SRAM Pin1] et [A15 SRAM Pin21].

Je ne sais donc pas si cela signifie qu'il faut démettre MA18 et MA17 de A18 et A15 pour les reliés à WE et CS de la SRAM ou alors laisser en l'état et shunter pour ajouter WE et CS sans supprimer A18 et A15.

Pour couronner le tout, n'ayant plus de SRAM, j'ai retirer la dernière qui était dans ma MoonSound.

Je voudrais éviter de la cramer juste en faisant des essais hasardeux.

Vais attendre et voir si je trouve plus d'infos, autrement, j'en resterai là pour le moment.

En l'état, effectivement, une SCC se limite à 512Ko de mapper.

Mais avec le Trio LS74(modifié) + LS08(ajouté) + LS139(ajouté), on doit arriver à "Basculer" d'une Mémoire à une autre.

Le problème est de savoir comment le faire.

Par exemple, je viens tout juste de Monter une SRAM en gigogne tous les signaux en parallèles sauf [WE SRAM Pin 29] et [CS SCRAM Pin22] qui doivent recevoir respectivement [MA18 SCC Pin40] et [MA17 SCC Pin39].

Le problème est que puisque les 2 SRAM sont branchées en parallèles, [MA18 SCC Pin40] et [MA17 SCC Pin39] sont déjà connectés respectivement sur [A18 SRAM Pin1] et [A15 SRAM Pin21].

Je ne sais donc pas si cela signifie qu'il faut démettre MA18 et MA17 de A18 et A15 pour les reliés à WE et CS de la SRAM ou alors laisser en l'état et shunter pour ajouter WE et CS sans supprimer A18 et A15.

Pour couronner le tout, n'ayant plus de SRAM, j'ai retirer la dernière qui était dans ma MoonSound.

Je voudrais éviter de la cramer juste en faisant des essais hasardeux.

Vais attendre et voir si je trouve plus d'infos, autrement, j'en resterai là pour le moment.

Voici le montage en gigogne:

Comme je le disais un peu plus haut, toutes les pins sont branchées en parallèle avec l'autre SRAM sauf CS et WE qui sont (pardonnez moi l’expression lol) "Pin en l'air"

Comme je le pensai, j'ai chargé SpaceManbow et lancé sans aucun problème malgré le jumelage des deux SRAM

Pour le moment, je n'ai pas encore touché aux LS ne sachant pas très exactement ce qu'il faut faire. Edité par igal Le 27/05/2013 à 19h34

Comme je le disais un peu plus haut, toutes les pins sont branchées en parallèle avec l'autre SRAM sauf CS et WE qui sont (pardonnez moi l’expression lol) "Pin en l'air"

Comme je le pensai, j'ai chargé SpaceManbow et lancé sans aucun problème malgré le jumelage des deux SRAM

Pour le moment, je n'ai pas encore touché aux LS ne sachant pas très exactement ce qu'il faut faire. Edité par igal Le 27/05/2013 à 19h34

Un peu cochon tes pates soudé ensemble

ce que tu aurais du faire, c'est de mettre les pates en l'air et ceux du dessous soudé sur celui du dessus. Les pin de la sram du dessus tu les replis sur la puce, c'est plus propre

des que tu as le schemas complet, je te le repique

edit: pense aussi a racourcir les pates en l'air pour les fils ! Edité par MSXlegend Le 27/05/2013 à 20h24

ce que tu aurais du faire, c'est de mettre les pates en l'air et ceux du dessous soudé sur celui du dessus. Les pin de la sram du dessus tu les replis sur la puce, c'est plus propre

des que tu as le schemas complet, je te le repique

edit: pense aussi a racourcir les pates en l'air pour les fils ! Edité par MSXlegend Le 27/05/2013 à 20h24

Mon Github ->[/b] github.com/msxlegend

challenge 2013 -> neodream MSX 2013

Concepteur du -> KCX Bluetooth transmitter

Demo Terminator2 T2.zip

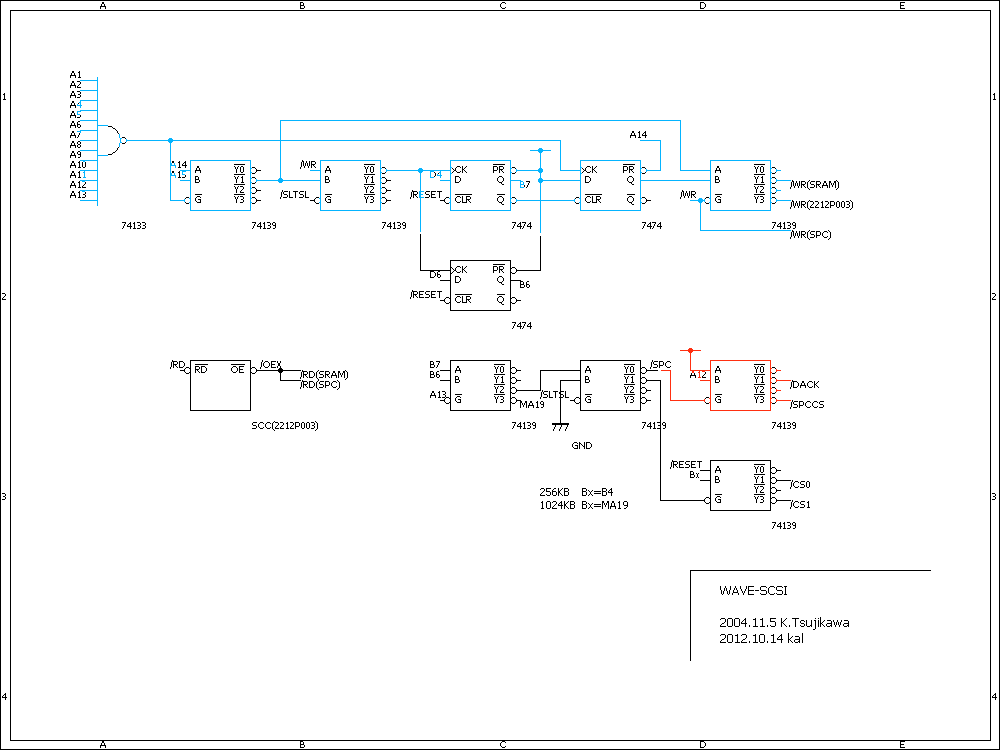

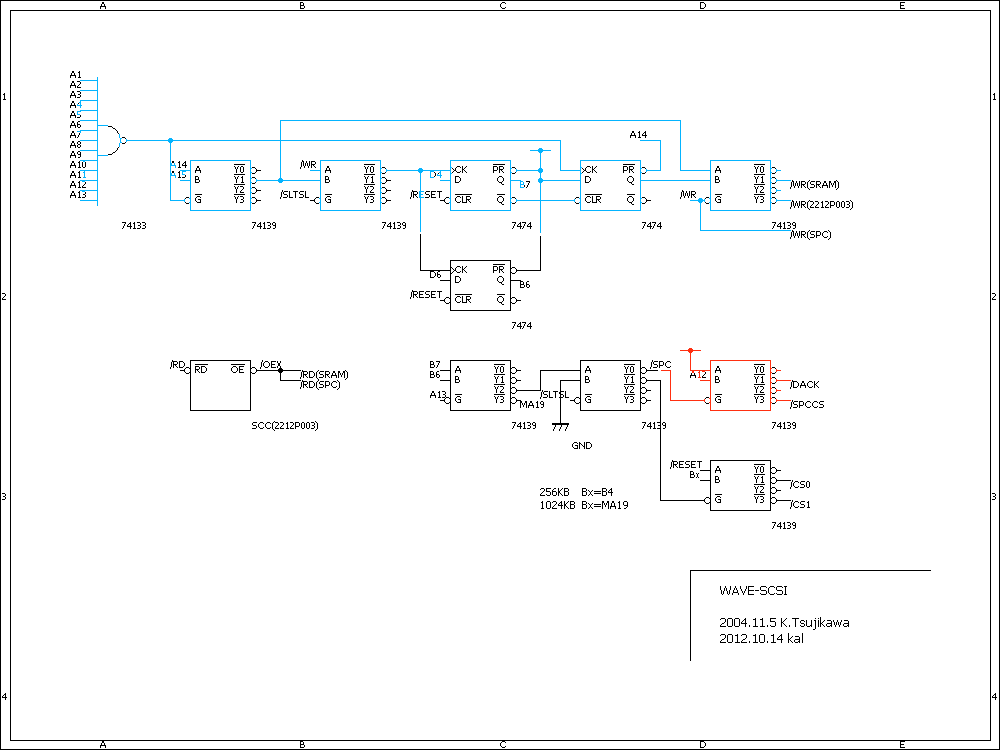

voici un site avec 2 schéma pour la wave SCSI

http://2nd.geocities.jp/k9412101/doc/ram_scsi.html

le second est plus intéressant car se rapproche plus de la mega scc mais lire le commentaire en gras

a develloper plus tard

traduction google du texte

◎ je joue avec Megakon

Contrôleur de ROM Mega, pour faire court "Megakon!" ! Je dois jouer avec, comme (CSC avec) ASC1 ~ 4,2212 P003. Je roulais à faire pseudo-RAM court. Finalement, je l'ai fait pour Megakon propre.

Schéma de principe de la Megakon self-made

◎ je tombe dans MEGA-SCSI

Après avoir sérieusement faire pseudo RAM follement, est MEGA-SCSI de folie. Sentiment d'accomplissement au moment de la normale de travail et cadre de travail ainsi était insupportable.

Il deviendra un regard lointain involontairement comme "Naa accro" Si vous regardez mon propre MEGA-SCSI sans l'utilisation prévue is're rouler quelque chose d'individuel.

Schéma de principe de l'onde-SCSI

* Faites partie mauvaise B7, B6 → B7 ', B6' de. Ceux qui sont inquiets, veuillez essayer de recréer dans la référence HC74 le schéma de circuit de la pseudo-SCC.

→ J'ai essayé de recréer dans le HC74. Cependant, le comportement n'est pas confirmée.

Schéma de principe d'une version modifiée de WAVE-SCSI

◎ Je me bats avec les périphériques

Vous pouvez créer mappeur de mémoire, vous pouvez obtenir périphériques fabriqués dans des pays étrangers, nous pouvons utiliser le périphérique mineur. Rien de tout cela était intéressant mais, comme cassé comme fatigué, quand je pars, il a été vendu ou quoi que ce soit, il a disparu Oita frère (

Actuellement, je suis calme et RS232C de SUNRISE MEGA-SCSI + adaptateur CF-SCSI + Micro Drive.

Schéma du mappeur car

Schéma de kal mapper

◎ Il est troublé intacte

Travail original de la CPS, comme une RAM avec MEGA-SCSI. Quelqu'un, tu ne faut pas faire avec la liberté de primaire et de travail élevée des écoles? Ou (Muri

L'œuvre originale de la CPS, il semble être en mesure de le faire quelqu'un dans le FPGA liés. RAM avec MEGA-SCSI, c'est OK si vous faites une fente d'expansion court. kal, chaleur MSX est parti froid, je n'ai pas l'énergie de faire, je suis désolé.

* Je ne suis travail électronique a repris fin Myo, mais ne peuvent pas le faire. Ne pas faire (?

◎ ceux réalisés

Eve de gong Mega?

Je me sens était "Dragon Quest" sera l'original. Gigli est trop.

Ce qui est impossible?

C'est un MEGA-SCSI de "ASC4". Je pense qu'il n'est pas seulement fait kal de cette volonté.

L'utilisation efficace?

est kal mapper. C'est un bon sentiment, si vous la mémoire (carte) ASC3 mappeur.

http://2nd.geocities.jp/k9412101/doc/ram_scsi.html

le second est plus intéressant car se rapproche plus de la mega scc mais lire le commentaire en gras

a develloper plus tard

traduction google du texte

◎ je joue avec Megakon

Contrôleur de ROM Mega, pour faire court "Megakon!" ! Je dois jouer avec, comme (CSC avec) ASC1 ~ 4,2212 P003. Je roulais à faire pseudo-RAM court. Finalement, je l'ai fait pour Megakon propre.

Schéma de principe de la Megakon self-made

◎ je tombe dans MEGA-SCSI

Après avoir sérieusement faire pseudo RAM follement, est MEGA-SCSI de folie. Sentiment d'accomplissement au moment de la normale de travail et cadre de travail ainsi était insupportable.

Il deviendra un regard lointain involontairement comme "Naa accro" Si vous regardez mon propre MEGA-SCSI sans l'utilisation prévue is're rouler quelque chose d'individuel.

Schéma de principe de l'onde-SCSI

* Faites partie mauvaise B7, B6 → B7 ', B6' de. Ceux qui sont inquiets, veuillez essayer de recréer dans la référence HC74 le schéma de circuit de la pseudo-SCC.

→ J'ai essayé de recréer dans le HC74. Cependant, le comportement n'est pas confirmée.

Schéma de principe d'une version modifiée de WAVE-SCSI

◎ Je me bats avec les périphériques

Vous pouvez créer mappeur de mémoire, vous pouvez obtenir périphériques fabriqués dans des pays étrangers, nous pouvons utiliser le périphérique mineur. Rien de tout cela était intéressant mais, comme cassé comme fatigué, quand je pars, il a été vendu ou quoi que ce soit, il a disparu Oita frère (

Actuellement, je suis calme et RS232C de SUNRISE MEGA-SCSI + adaptateur CF-SCSI + Micro Drive.

Schéma du mappeur car

Schéma de kal mapper

◎ Il est troublé intacte

Travail original de la CPS, comme une RAM avec MEGA-SCSI. Quelqu'un, tu ne faut pas faire avec la liberté de primaire et de travail élevée des écoles? Ou (Muri

L'œuvre originale de la CPS, il semble être en mesure de le faire quelqu'un dans le FPGA liés. RAM avec MEGA-SCSI, c'est OK si vous faites une fente d'expansion court. kal, chaleur MSX est parti froid, je n'ai pas l'énergie de faire, je suis désolé.

* Je ne suis travail électronique a repris fin Myo, mais ne peuvent pas le faire. Ne pas faire (?

◎ ceux réalisés

Eve de gong Mega?

Je me sens était "Dragon Quest" sera l'original. Gigli est trop.

Ce qui est impossible?

C'est un MEGA-SCSI de "ASC4". Je pense qu'il n'est pas seulement fait kal de cette volonté.

L'utilisation efficace?

est kal mapper. C'est un bon sentiment, si vous la mémoire (carte) ASC3 mappeur.

en bleu ce qui existe déja dans la megasram scc

en noir ce qu'il ajouter pour avoir 1024k

en rouge ce qu'il faut ajouter pour le controleur scsi

ce schéma a le mérite de ne pas toucher au montage d'origine mais juste de faire des ajouts

en noir ce qu'il ajouter pour avoir 1024k

en rouge ce qu'il faut ajouter pour le controleur scsi

ce schéma a le mérite de ne pas toucher au montage d'origine mais juste de faire des ajouts

N'est-il pas plus intéressant de faire une mega-sram ascii qui elle support les 1024Ko et voir même 2048Ko sans broncher? Elle permet aussi de faire un sram-disk sauvegardable 3 semaines avec un supercondensateur de 1F. Il est possible mettre un permutateur pour sélectionner le type de mapper (8 ou 16Ko).

@Igal voici un lien vers les fichiers du Gal de Kal qui remplace les LS , bon je sais sans tout les fils ca fait moins joli et ca manque de couleur :

http://2nd.geocities.jp/k9412101/src/wvscsi2_gal.txt

http://2nd.geocities.jp/k9412101/src/wvscsi2_jed.txt

@Jipe : pour info si tu veux jouer aussi il me semble t avoir laisse des GAL16V8 donc tu n a plus qu a les programmer Edité par TheWhipMaster Le 01/06/2013 à 18h07

http://2nd.geocities.jp/k9412101/src/wvscsi2_gal.txt

http://2nd.geocities.jp/k9412101/src/wvscsi2_jed.txt

@Jipe : pour info si tu veux jouer aussi il me semble t avoir laisse des GAL16V8 donc tu n a plus qu a les programmer Edité par TheWhipMaster Le 01/06/2013 à 18h07

HB-F700F(X2),A1GT,Altera DE1 + slots , Sunrise IDE CF,FMPAC, Music Module,Slot expander 8X (X3) ,PlaySoniq, et autres

Un GAL (Generic array logic) ça se programme comme une Eprom?

Ce Gal est donc capable de simuler le comportement "global' de l'ensemble des signaux traités par les 3 LS utilisés.

Ca peut être une solution très pratique.

Je vais déjà essayer de sortir une implantation (en début de semaine) selon le schéma que nous à trouvé Jipe

Ce Gal est donc capable de simuler le comportement "global' de l'ensemble des signaux traités par les 3 LS utilisés.

Ca peut être une solution très pratique.

Je vais déjà essayer de sortir une implantation (en début de semaine) selon le schéma que nous à trouvé Jipe

Perso j ouvre l interface de mon programmeur (Hi-lo all-11) je sélectionne GAL il me demande le fichier et zou c'est parti... oui j utilise des outils pour assisté

HB-F700F(X2),A1GT,Altera DE1 + slots , Sunrise IDE CF,FMPAC, Music Module,Slot expander 8X (X3) ,PlaySoniq, et autres

Répondre

Vous n'êtes pas autorisé à écrire dans cette catégorie