L'atelier [EN COURS] Méga S-Ram SCC => 1024 => Wave SCSI Convertion d'une mégaSramSCC en Wave SCSI

Reprise du message précédent

A la demande générale de SVEN

Voila de quoi s'éclater les yeux.

(Je cherche des couleurs phosphorescentes, vais finir par trouver

)

)

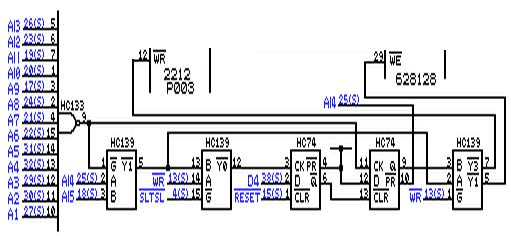

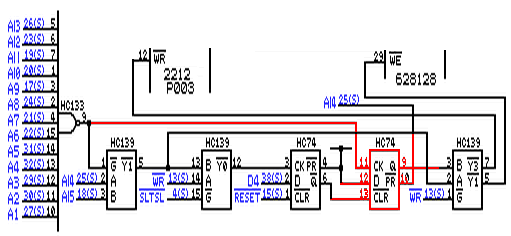

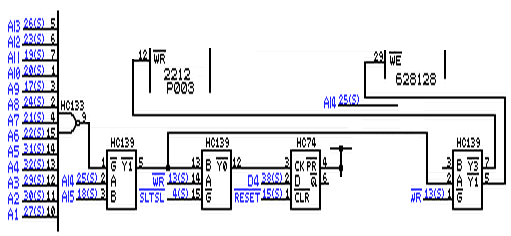

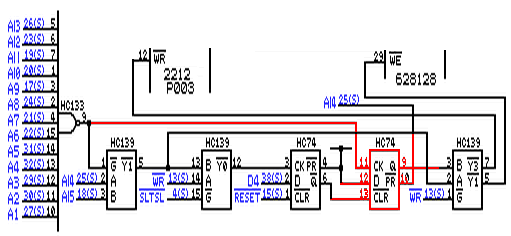

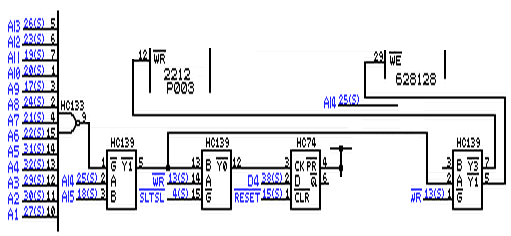

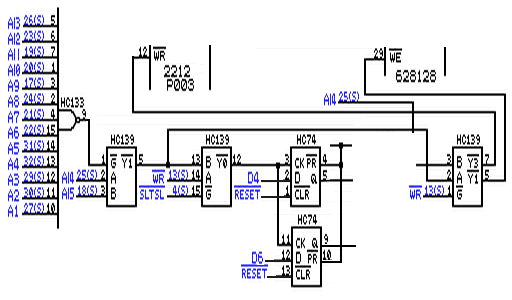

1) Le LS139 encadré sur la droite ne peut pas convenir au complément WAVESCSI à cause de la porte B en Pin 3 occupée par un signal venant de LS74 la porte Q Pin 9.

2) Le reste des signaux dans ce même encadré sont tous bons et permettent un repiquage Pin sur Pin

3) J'ai mis dans un tableau (à droite) ce qui semble être les différentes combinaisons possibles.

4) La combinaison actuelle (donnée par défaut) semble être celle nommée ALPHA.

5) Il est tout à fait possible que certaines/toutes combinaisons "ALPHA",et/ou "BETA" et/ou "GAMA" et/ou "DELTA" et/ou "GAMA" aient besoin d'une intervention supplémentaire sur la SCC (peut être comme indiqué en haut du tableau

)

)Encore un peu flou tout ça...

Personne parle Japonais?

@TheWipeMaster: T'as pas une idée précise de ce qu'il faut "combiner" ?

Peux tu jeter un oeil sur le post du 24/12/11 à 18h57 dans un petit cercle rouge! Je voudrais savoir si il y a une erreur, ou pas?

Chli....mblic...

Edit: Pour passer la MégaSRam SCC 512 en MégaSRam SCC 1024!

Il faut juste ajouter une seconde SRam 512 ou alors faut chercher une toute autre S-Ram? Edité par igal Le 27/12/2011 à 17h29

Avant de perdre les caractères :

Le truc à côté de WAVE-SCSI, c'est "Schematic reference"

Juste au dessus, nous avons :

BxはSRAM容量に合わせてB4,B5,MA19を使用

Y'a PAS LE KANJI !! J'espère que le lien sera lisible. En fait SI, mais pas dans la prévisualisation ...

[url=http://translate.google.fr/#ja|en|MSXVillage.fr%20%3A%0ABx%E3%81%AFSRAM%E5%AE%B9%E9%87%8F%E3%81%AB%E5%90%88%E3%82%8F%E3%81%9B%E3%81%A6B4%2CB5%2CMA19%E3%82%92%E4%BD%BF%E7%94%A8%0A][/url]

je ne sais plus si la direction des virgules a une signification particulière.

Je continue dès que j'ai un peu de temps. (Edit : finalement non, j'ai changé d'avis !! :-) )

Et faut que je repose mes yeux, hein Igal !! Edité par

SveN

Le 27/12/2011 à 20h01

Edité par

SveN

Le 27/12/2011 à 20h01

Le truc à côté de WAVE-SCSI, c'est "Schematic reference"

Juste au dessus, nous avons :

BxはSRAM容量に合わせてB4,B5,MA19を使用

Y'a PAS LE KANJI !! J'espère que le lien sera lisible. En fait SI, mais pas dans la prévisualisation ...

[url=http://translate.google.fr/#ja|en|MSXVillage.fr%20%3A%0ABx%E3%81%AFSRAM%E5%AE%B9%E9%87%8F%E3%81%AB%E5%90%88%E3%82%8F%E3%81%9B%E3%81%A6B4%2CB5%2CMA19%E3%82%92%E4%BD%BF%E7%94%A8%0A][/url]

je ne sais plus si la direction des virgules a une signification particulière.

Je continue dès que j'ai un peu de temps. (Edit : finalement non, j'ai changé d'avis !! :-) )

Et faut que je repose mes yeux, hein Igal !!

Edité par

SveN

Le 27/12/2011 à 20h01

Edité par

SveN

Le 27/12/2011 à 20h01

Philips.NMS.8245/50/80, Sony.F1XV/HBF-700D, Pana.FSA1FX/A1WX(x2)/A1GT, OCM, GR8BIT.... et ...

B4 Bx is according to the capacity SRAM, B5, using the MA19

GDX a déja fait la traduction en bon français

GDX a déja fait la traduction en bon français

Citation :

/OEX ressemble au /SLTS mais lors d'un accès mémoire d’une vague SCC (9800~9FFFh du bank 3Fh), ça ne devient pas "L".

Bx utilise B4, B9, MA19 en fonction de la taille de la SRAM

RAM = Lors d'un accès à la SRAM, "H". Lors d'un accès SPC, "L".

MA19 = N'est pas relié (inutilisé) si inférieur ou égal à 512Ko.

Bx utilise B4, B9, MA19 en fonction de la taille de la SRAM

RAM = Lors d'un accès à la SRAM, "H". Lors d'un accès SPC, "L".

MA19 = N'est pas relié (inutilisé) si inférieur ou égal à 512Ko.

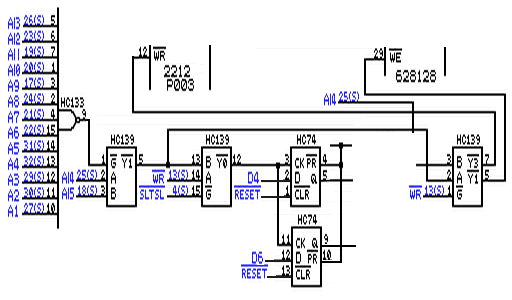

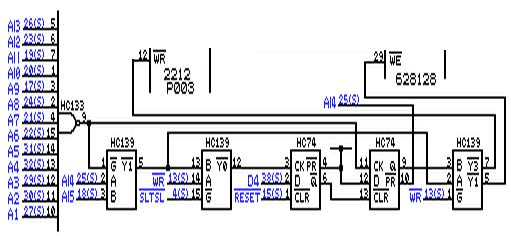

il ne faut pas ajouter de 74LS74 il suffit de décabler la porte et de la recabler

attention pour la porte avec le signal D4 on utilise Q a la place de /Q

aprés il reste a intercaler les portes LS08

une interrogation subsiste :

Mega SRAM /Y1 du LS139 vers /WE de la SRAM /Y3 vers /WR de la puce SCC

Wave SCC /Y3 du LS139 vers /WE de la SRAM /Y1 vers /WR de la puce SCC

attention pour la porte avec le signal D4 on utilise Q a la place de /Q

aprés il reste a intercaler les portes LS08

une interrogation subsiste :

Mega SRAM /Y1 du LS139 vers /WE de la SRAM /Y3 vers /WR de la puce SCC

Wave SCC /Y3 du LS139 vers /WE de la SRAM /Y1 vers /WR de la puce SCC

Jipe :

GDX a déja fait la traduction en bon français

Citation :

/OEX ressemble au /SLTS mais lors d'un accès mémoire d’une vague SCC (9800~9FFFh du bank 3Fh), ça ne devient pas "L".

Ici, j'aurais dû sans doute mettre :

/OEX ressemble au /SLTS mais lors d'un accès mémoire de la Wave SCC (9800~9FFFh du bank 3Fh), ça ne devient pas "L".

regarde un datasheet de 74LS74 il y a 2 sorties par porte une Q et une /Q il faut juste ne pas se tromper car tout n'est pas renseigné sur le schéma de la mega SCC et il n'y a pas les numéros des pattes sur le schéma de la Wave

pour le cerveau désolé je peux rien faire

pour le cerveau désolé je peux rien faire

Citation :

Peux tu jeter un oeil sur le post du 24/12/11 à 18h57 dans un petit cercle rouge! Je voudrais savoir si il y a une erreur, ou pas?

@Igal: Bonne annee Igal, J'ai réaligné les pins et nom pour simplifier la comparaison avec la mega scsi standard voir poste sur le sujet "Fabriquer sa Mega-SCSI" Le 07/12/11 à 17h59 ... Il faut bien faire attention a U5 pour spc ver spccs et Dack

HB-F700F(X2),A1GT,Altera DE1 + slots , Sunrise IDE CF,FMPAC, Music Module,Slot expander 8X (X3) ,PlaySoniq, et autres

Thx TheWipeMaster

Peut être qu'il est possible d'implanter en gigogne 2 X 512Ko comme c'est le cas avec les 2 X 128Ko

Vais zieuter ça comme il faut et adapter au Wave-Scsi

Edité par

igal

Le 03/01/2012 à 13h20

Edité par

igal

Le 03/01/2012 à 13h20

Un grand merci à Sven pour le tant recherché MB89352AP

La lettre Max à l'air d'être passée sous un rouleau compresseur

Finalement, rien de bien méchant, j'ai pu redresser les Pins à la Pince à Bec...

Ca fait quand même plaisir d'avoir de quoi se mettre sous la dent.

Je suis ton débiteur l'ami

La lettre Max à l'air d'être passée sous un rouleau compresseur

Finalement, rien de bien méchant, j'ai pu redresser les Pins à la Pince à Bec...

Ca fait quand même plaisir d'avoir de quoi se mettre sous la dent.

Je suis ton débiteur l'ami

Dans le sujet relatif à la création d'une MegaSCSI, TheWhipMaster a posté l'image d'une WaveSCSI 1024K. Quelles sont les modifications à apporter pour passer de 512 à 1024K ? Et quel composant utiliser ?

Il me démange de saboter quelques cartouches ... mais à défaut de disposer de l'ensemble des composants ... je prends des notes, d'innombrables notes !!

Il me démange de saboter quelques cartouches ... mais à défaut de disposer de l'ensemble des composants ... je prends des notes, d'innombrables notes !!

Philips.NMS.8245/50/80, Sony.F1XV/HBF-700D, Pana.FSA1FX/A1WX(x2)/A1GT, OCM, GR8BIT.... et ...

Salut Sven.

Pour les 1024, il faut 2 X 512 comme celles ci => SRAM HM628512

J'en ai acheté une ici le port est gratuit => http://cgi.ebay.fr/IC-HM628512ALP-7-DIP-32-HM628512-/310303024609?pt=LH_DefaultDomain_0&hash=item483f8065e1

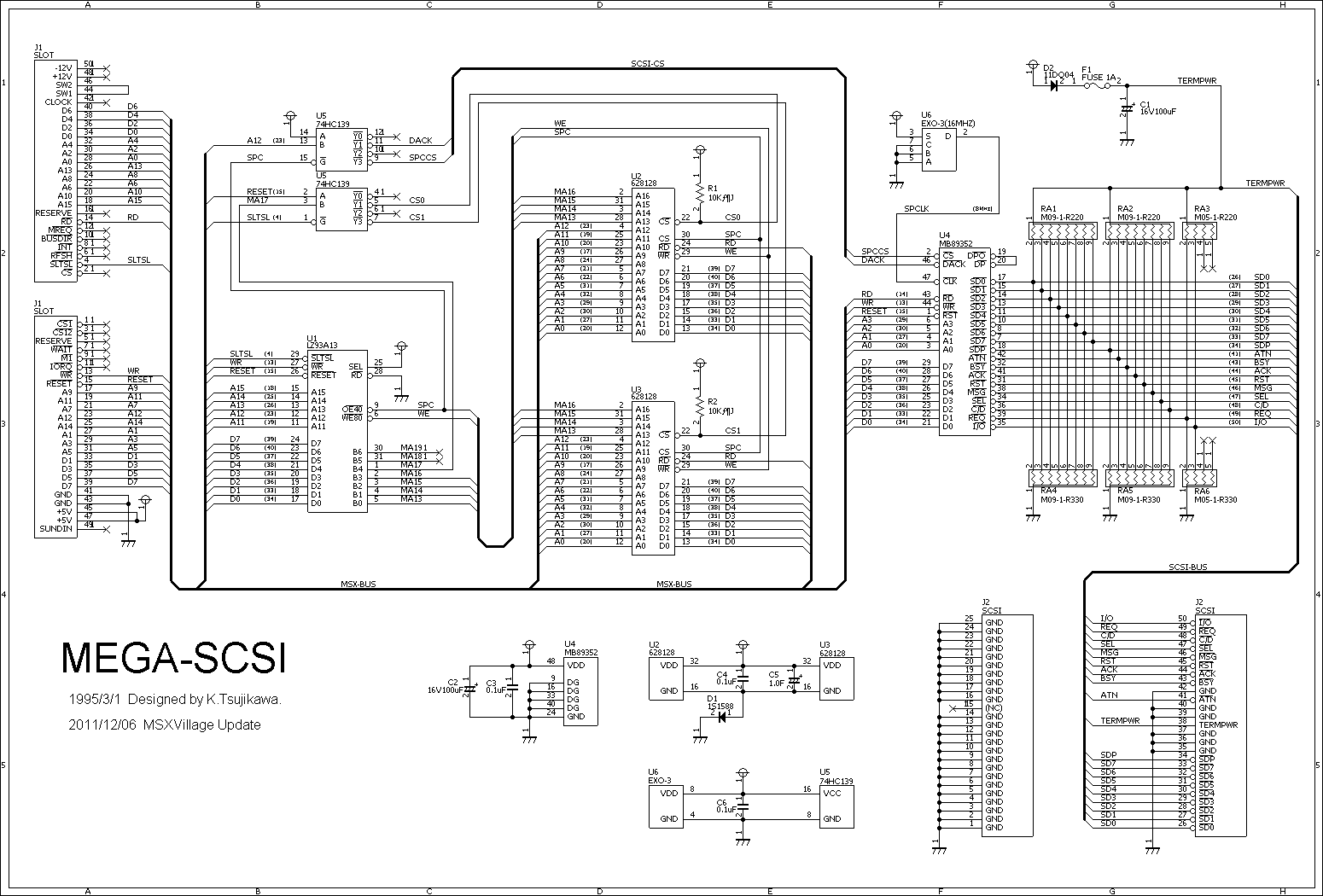

Juste CS0 et CS1 qui doit dire quel Chips est actif que ce soit une paire de:

128 X 2 => Schéma complet sur le MégaScsi => http://www.msxvillage.fr/upload/megascsi.bmp

256 X 2 => il faut juste cabler le MA17 sur la mémoire et remplacer le signal MA17 par MA18 pour génerer les CS0 CS1 sur le 3 du HC139 (Source Jipe)

512 X 2 => ???

Il me semble (au conditionnel donc) que les MA sont nécessaire pour "driver" les données.

La SCC génère les signaux:

MA 13

MA 14

MA 15

MA 16

MA 17

MA 18

MA 19 est donc créé en combinant les signaux B6', B7' et A13

MA 19 est déjà présent sur LZ93A13 et ne nécessite donc pas de [HC08 (B6' + B7')]

La question reste posé pour le câblage complet 512 X 2

Pour les 1024, il faut 2 X 512 comme celles ci => SRAM HM628512

J'en ai acheté une ici le port est gratuit => http://cgi.ebay.fr/IC-HM628512ALP-7-DIP-32-HM628512-/310303024609?pt=LH_DefaultDomain_0&hash=item483f8065e1

Juste CS0 et CS1 qui doit dire quel Chips est actif que ce soit une paire de:

128 X 2 => Schéma complet sur le MégaScsi => http://www.msxvillage.fr/upload/megascsi.bmp

256 X 2 => il faut juste cabler le MA17 sur la mémoire et remplacer le signal MA17 par MA18 pour génerer les CS0 CS1 sur le 3 du HC139 (Source Jipe)

512 X 2 => ???

Il me semble (au conditionnel donc) que les MA sont nécessaire pour "driver" les données.

La SCC génère les signaux:

MA 13

MA 14

MA 15

MA 16

MA 17

MA 18

MA 19 est donc créé en combinant les signaux B6', B7' et A13

MA 19 est déjà présent sur LZ93A13 et ne nécessite donc pas de [HC08 (B6' + B7')]

La question reste posé pour le câblage complet 512 X 2

la sram 256k n'existe pas celle qui est vendue est de 32kx8 = 256 k bit

on peut donc faire les montages suivants

128k

256k = 128k x 2

512k

1024k = 512k x2

donc lire

512k X 2 => il faut juste cabler le MA17 sur la mémoire et remplacer le signal MA17 par MA18 pour génerer les CS0 CS1 sur le 3 du HC139 (Source Jipe)

on peut donc faire les montages suivants

128k

256k = 128k x 2

512k

1024k = 512k x2

donc lire

512k X 2 => il faut juste cabler le MA17 sur la mémoire et remplacer le signal MA17 par MA18 pour génerer les CS0 CS1 sur le 3 du HC139 (Source Jipe)

@Sven:

tout d'abord, voici le montage initial qui ne t'intéressera peut être pas, mais qu'il faut connaitre pour comprendre la suite des modifications

La face avant du PCB comporte aussi quelques modifications, mais si tu souhaites les voir voici le lien => http://www.msxvillage.fr/forum/topic.php?id=998&pt=1

Tu remarqueras que les 4 CI sont reliés par des traits en couleurs dont les angles sont courbés. (C'est pas ma signature ce genre de design )

)

74 HC 139 X 2

74 HC 133

74 HC 74

La partie intéressante est le 74 HC 74 qui va être modifié selon les directives de Jipe afin d'économiser l'ajout d'un second 74 HC 74.

A partir de là tout les nouveaux CI ainsi que le 74 HC 74 vont permettre de transformer la Méga SCSI en WAVE SCSI.

J'ai pris soin de faire des traits verts et angulaires.

1) La partie haute à savoir MB89352, EXO3 et IDC 50 est identique à celle que l'on retrouve sur le Méga SCSI.

2a) La partie Basse qui contient la SCC (Face cachée) correspond au LZ93A13. (Avec MA 17 et MA 18 en moins)

2b) La partie Basse visible contient les LS (74 HC 139 X 2, 74 HC 133, 74 HC 74) qui gèrent la RAM tout le fait le LS139 sur la Méga S-RAM.

3) La partie intermédiaire ( 74 HC 08, 74 HC 139 et 74 HC 74 modifié) ont pour tache de générer les signaux:

B6', B7', A13, /WR(SRAM), /WR(SCC), et /WR(SPC)

Pour rappel voici le DataSheet du 74 HC 139

Ces trois signaux doivent être connectés au même endroit quel que soit la quantité de S-RAM monté.

/WR(SRAM) => WR de la S-Ram Pin 29 (Identique sur 128 et 512 ?)

/WR(SCC) => WR de la SCC Pin 12

/WR(SPC) => WR de la MB89352 Pin 44

Les trois signaux suivants ne sont pas encore très clair dans mon esprit.

Si il y a vraiment une similitude entre les signaux utiles pour le Méga SCSI et le WAVE SCSI, il suffit de connaitre la correspondance de ces trois derniers pour appliquer la même logique. (Hypothétiquement )

)

B6' => MA 18 ?

B7' => MA 19 ?

A13 => 74 HC 139 Pin 1 ( Dépend de la combinaison choisi 128 X1 ou 128 X 2 ou 512 X 1 ou encore 512 X 2 ?)

Voilà l'ami je suis pas allé plus loin dans le WAVE SCSI.

Il doit y avoir pas mal d'erreurs dans mes suppositions, mais attendons la voix de la Sagesse pour savoir Précisément

tout d'abord, voici le montage initial qui ne t'intéressera peut être pas, mais qu'il faut connaitre pour comprendre la suite des modifications

La face avant du PCB comporte aussi quelques modifications, mais si tu souhaites les voir voici le lien => http://www.msxvillage.fr/forum/topic.php?id=998&pt=1

Tu remarqueras que les 4 CI sont reliés par des traits en couleurs dont les angles sont courbés. (C'est pas ma signature ce genre de design

)

)74 HC 139 X 2

74 HC 133

74 HC 74

La partie intéressante est le 74 HC 74 qui va être modifié selon les directives de Jipe afin d'économiser l'ajout d'un second 74 HC 74.

A partir de là tout les nouveaux CI ainsi que le 74 HC 74 vont permettre de transformer la Méga SCSI en WAVE SCSI.

J'ai pris soin de faire des traits verts et angulaires.

1) La partie haute à savoir MB89352, EXO3 et IDC 50 est identique à celle que l'on retrouve sur le Méga SCSI.

2a) La partie Basse qui contient la SCC (Face cachée) correspond au LZ93A13. (Avec MA 17 et MA 18 en moins)

2b) La partie Basse visible contient les LS (74 HC 139 X 2, 74 HC 133, 74 HC 74) qui gèrent la RAM tout le fait le LS139 sur la Méga S-RAM.

3) La partie intermédiaire ( 74 HC 08, 74 HC 139 et 74 HC 74 modifié) ont pour tache de générer les signaux:

B6', B7', A13, /WR(SRAM), /WR(SCC), et /WR(SPC)

Pour rappel voici le DataSheet du 74 HC 139

Ces trois signaux doivent être connectés au même endroit quel que soit la quantité de S-RAM monté.

/WR(SRAM) => WR de la S-Ram Pin 29 (Identique sur 128 et 512 ?)

/WR(SCC) => WR de la SCC Pin 12

/WR(SPC) => WR de la MB89352 Pin 44

Les trois signaux suivants ne sont pas encore très clair dans mon esprit.

Si il y a vraiment une similitude entre les signaux utiles pour le Méga SCSI et le WAVE SCSI, il suffit de connaitre la correspondance de ces trois derniers pour appliquer la même logique. (Hypothétiquement

)

)B6' => MA 18 ?

B7' => MA 19 ?

A13 => 74 HC 139 Pin 1 ( Dépend de la combinaison choisi 128 X1 ou 128 X 2 ou 512 X 1 ou encore 512 X 2 ?)

Voilà l'ami je suis pas allé plus loin dans le WAVE SCSI.

Il doit y avoir pas mal d'erreurs dans mes suppositions, mais attendons la voix de la Sagesse pour savoir Précisément

Répondre

Vous n'êtes pas autorisé à écrire dans cette catégorie