L'école le slot expander pour les nuls et son électronique

Yes Boss !!

j'ecoute et attend la suite ...

j'ecoute et attend la suite ...

TURBO-R FS-A1ST 512/128ko MSX2+ NMS 8250 F4 /Fix Audio /Ram 1/4Mb VDP9958 VRAM 192ko 2FDD SANYO WAVY PHC35J MSX2 NMS 8280 Ram 4Mb VDP9938 VRAM 192ko 2FDD NMS 8250 128/128ko 2FDD VG8235/39 128/128ko 1FDD SONY HB-F700D MSX1 MC810 32/16k VG 8020 64k HB75F 64k HX-22 64k RS232/ CX5M 32k HB501F EXT : My Exp 4X/[b] MegaFlashSCC 512ko/BERT R2/BEER CF/SUNRISE 2CF/FUNRICE V2.01/MAXIOL/MEGASCSI HDD-CD/SDMSX 1SD/FMPAC SRAM/NMS1205+1160/RS 232 Harukaze/GR8NET/DOS2/ HOMER V2 RAM512ko/Floppy Pack/MAXduino/ROM1664/FM Pak /GR8NET /AMIGA/ PC/ RaspB Pi(B) / ARDUINO

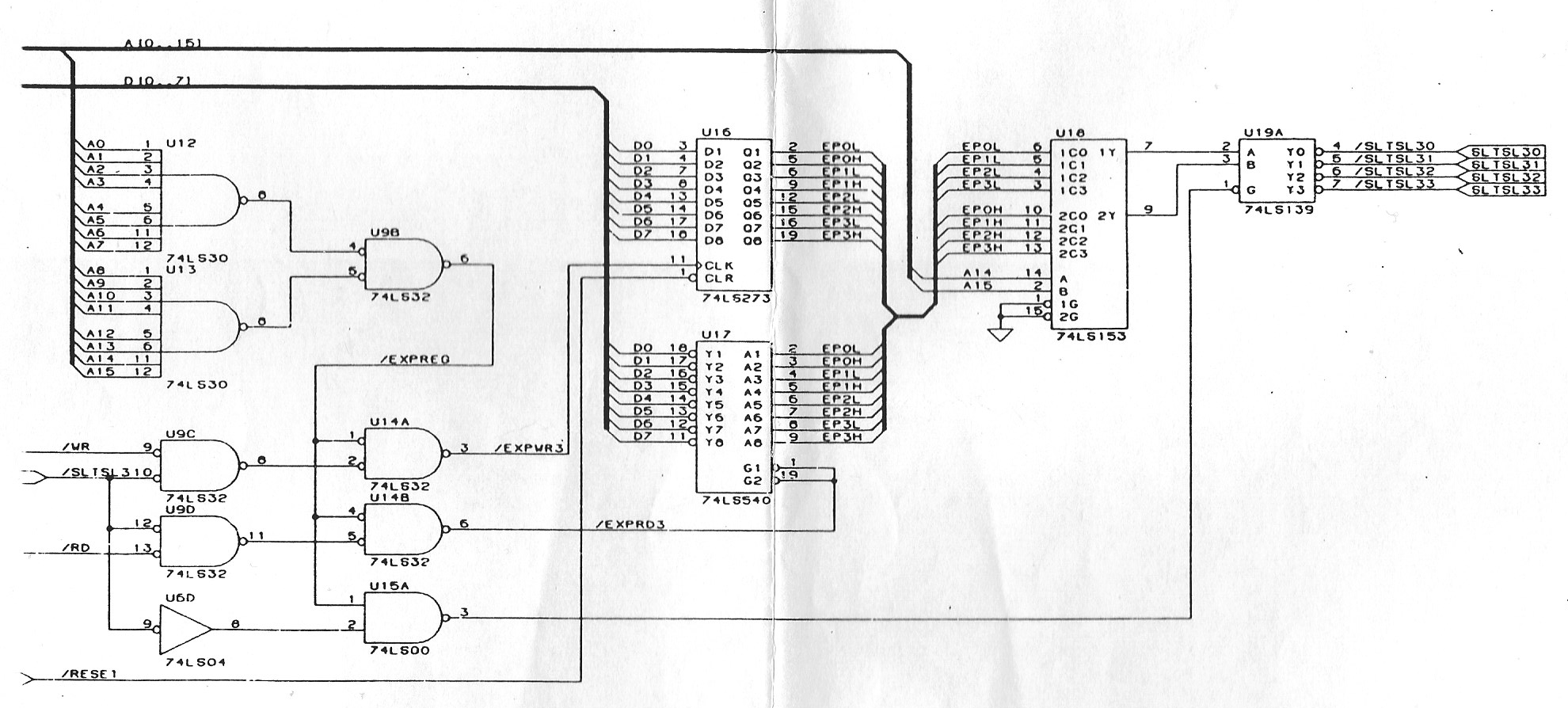

d'abord les portes simples :

le 74LS00 est donc une porte ET dont la sortie est inversée

le 74LS04 est un simple Inverseur

le 74LS30 est une porte ET à 8 entrées dont la sortie est inversée

le 74LS32 est une porte OU à 2 entrées

le 74LS00 est donc une porte ET dont la sortie est inversée

le 74LS04 est un simple Inverseur

le 74LS30 est une porte ET à 8 entrées dont la sortie est inversée

le 74LS32 est une porte OU à 2 entrées

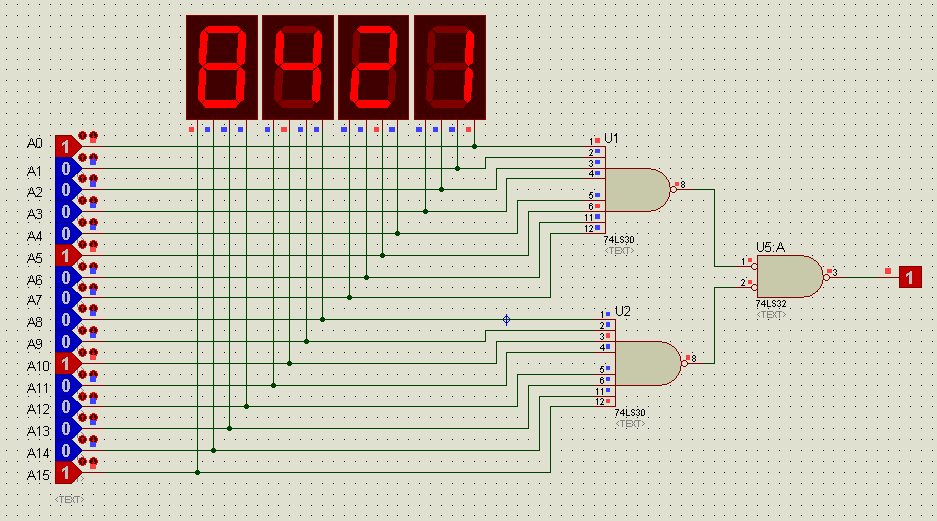

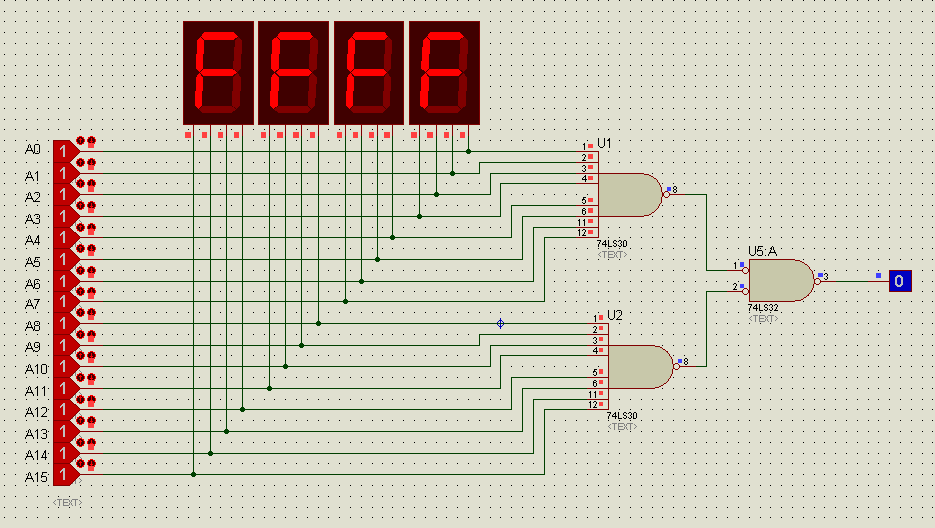

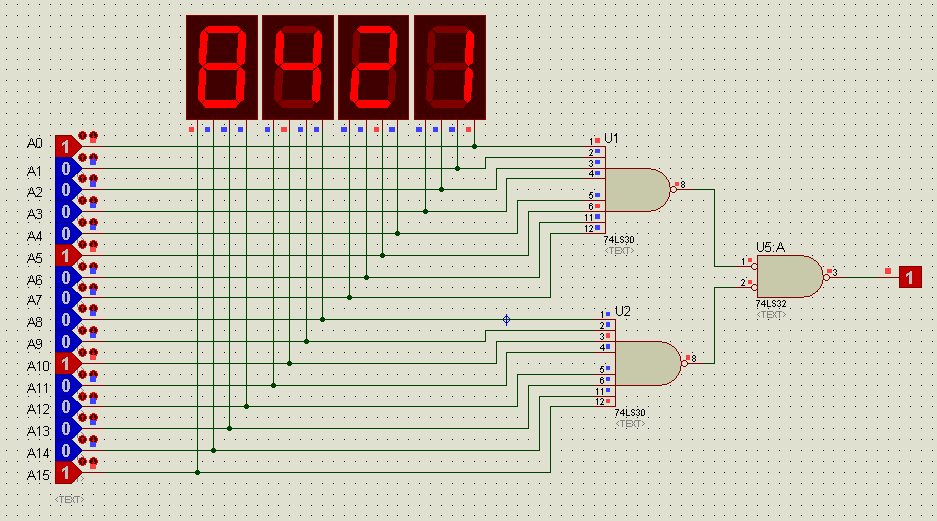

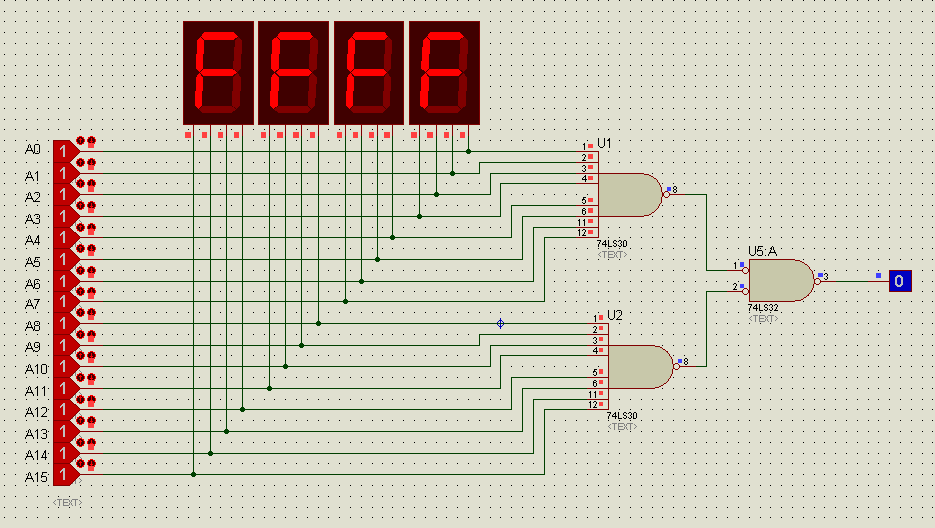

voici une simulation pour voir comment l'adresse FFFFh est décodée par le montage

1er cas l'adresse est différente de FFFFh la sortie du LS32 reste a 1

2éme l'adresse est égale à FFFFh la sortie du LS32 passe a 0

1er cas l'adresse est différente de FFFFh la sortie du LS32 reste a 1

2éme l'adresse est égale à FFFFh la sortie du LS32 passe a 0

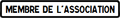

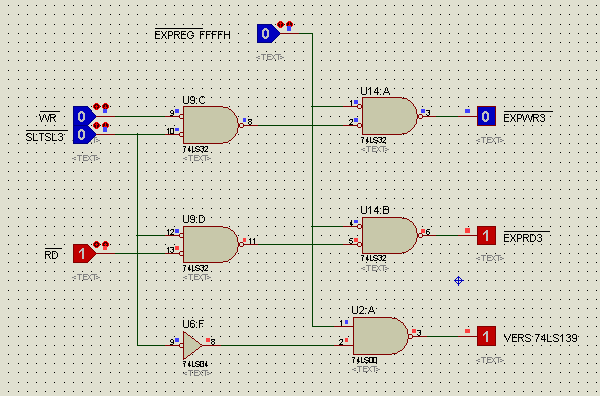

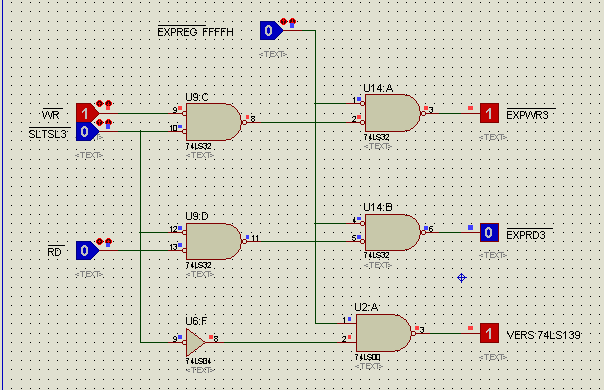

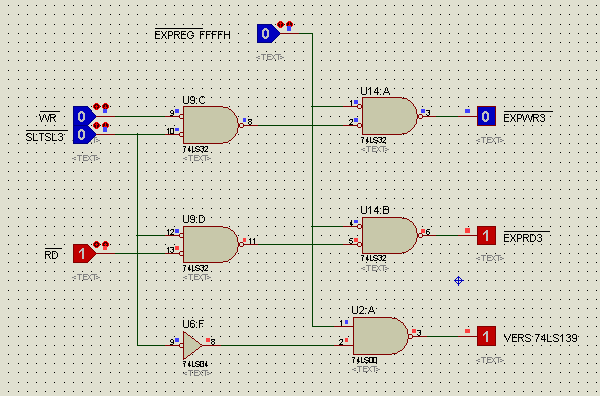

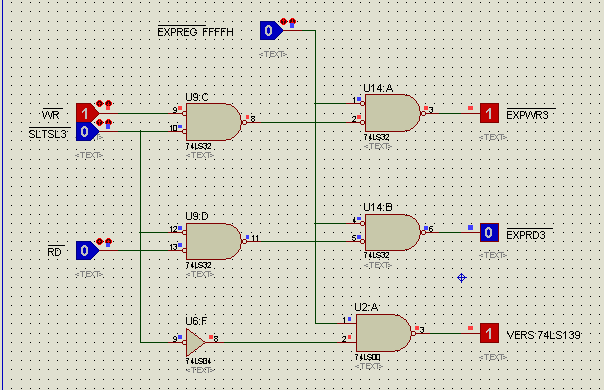

voici le décodage des portes qui gérent les signaux /SLTSL /RD et /WR

il faut savoir qu'un signal noté / est actif au niveau bas ( 0V )

en mode écriture

en mode lecture

a savoir que les signaux /RD et /WR ne peuvent jamais présents en même temps

il faut savoir qu'un signal noté / est actif au niveau bas ( 0V )

en mode écriture

en mode lecture

a savoir que les signaux /RD et /WR ne peuvent jamais présents en même temps

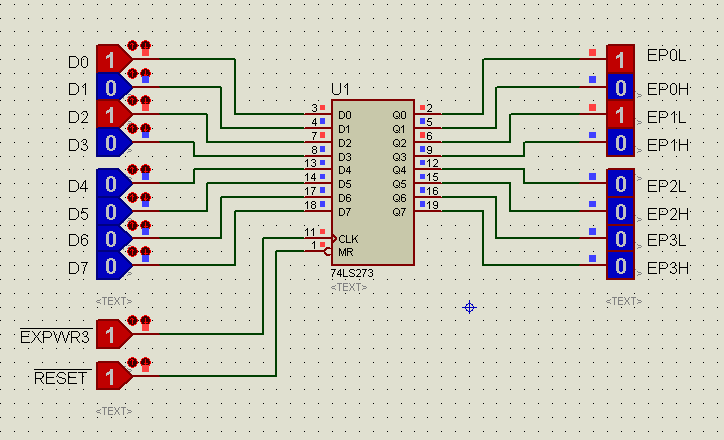

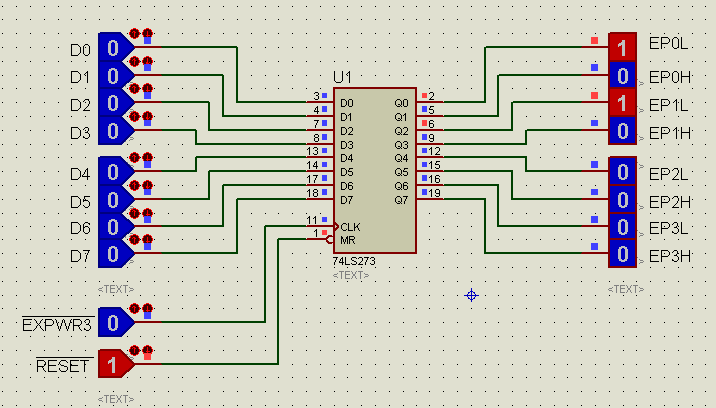

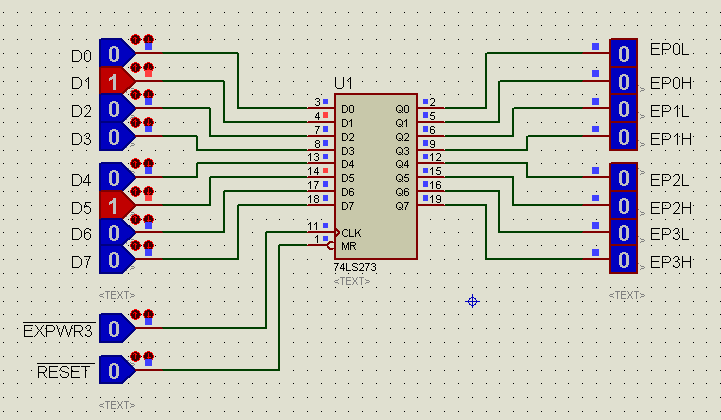

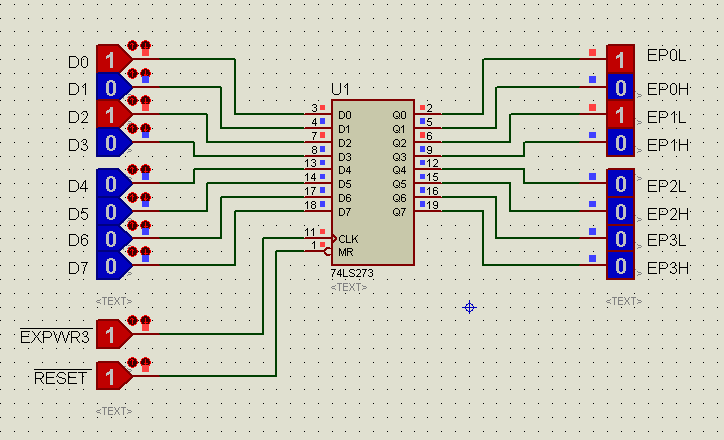

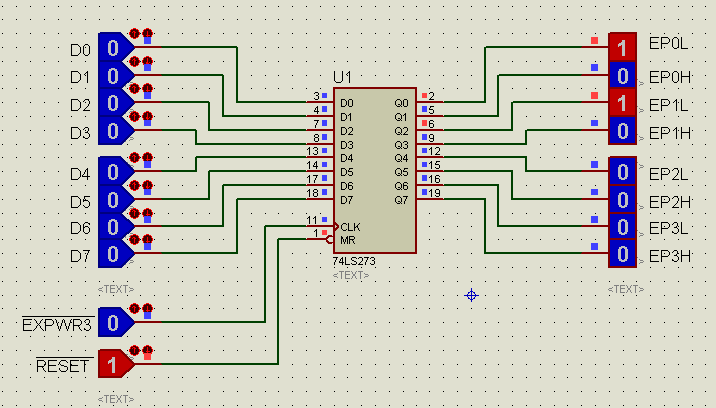

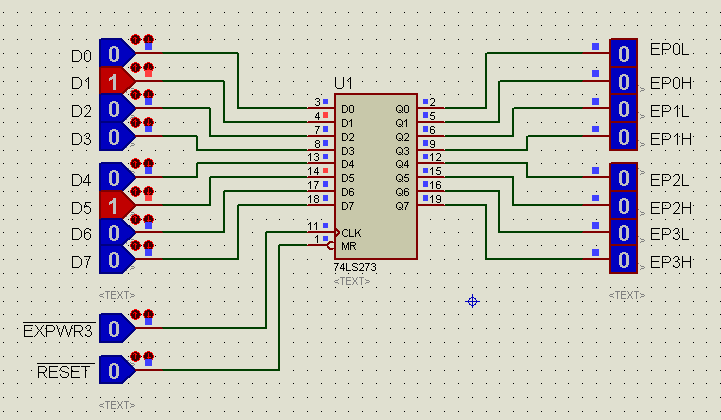

on va passer au 74LS273 qui est en quelque sorte une mémoire composée de plusieurs bascules Flip-flop

ce composant mémorise l'état des bits présents a son entrée par validation de son entrée clock

les sorties sont remises a 0 par MR qui est cablé sur le /RESET du MSX

voici l'écriture des données

leur mémorisation

et la remise à zéro sur reset quelque soit la valeur sur le bus de données

ce composant mémorise l'état des bits présents a son entrée par validation de son entrée clock

les sorties sont remises a 0 par MR qui est cablé sur le /RESET du MSX

voici l'écriture des données

leur mémorisation

et la remise à zéro sur reset quelque soit la valeur sur le bus de données

euh question le signal final sltsl 31/32/33/30 est il modifier si on y connecte quelque chose une rom et l'info reviens t elle a la source ??? via le ls30 ??

TURBO-R FS-A1ST 512/128ko MSX2+ NMS 8250 F4 /Fix Audio /Ram 1/4Mb VDP9958 VRAM 192ko 2FDD SANYO WAVY PHC35J MSX2 NMS 8280 Ram 4Mb VDP9938 VRAM 192ko 2FDD NMS 8250 128/128ko 2FDD VG8235/39 128/128ko 1FDD SONY HB-F700D MSX1 MC810 32/16k VG 8020 64k HB75F 64k HX-22 64k RS232/ CX5M 32k HB501F EXT : My Exp 4X/[b] MegaFlashSCC 512ko/BERT R2/BEER CF/SUNRISE 2CF/FUNRICE V2.01/MAXIOL/MEGASCSI HDD-CD/SDMSX 1SD/FMPAC SRAM/NMS1205+1160/RS 232 Harukaze/GR8NET/DOS2/ HOMER V2 RAM512ko/Floppy Pack/MAXduino/ROM1664/FM Pak /GR8NET /AMIGA/ PC/ RaspB Pi(B) / ARDUINO

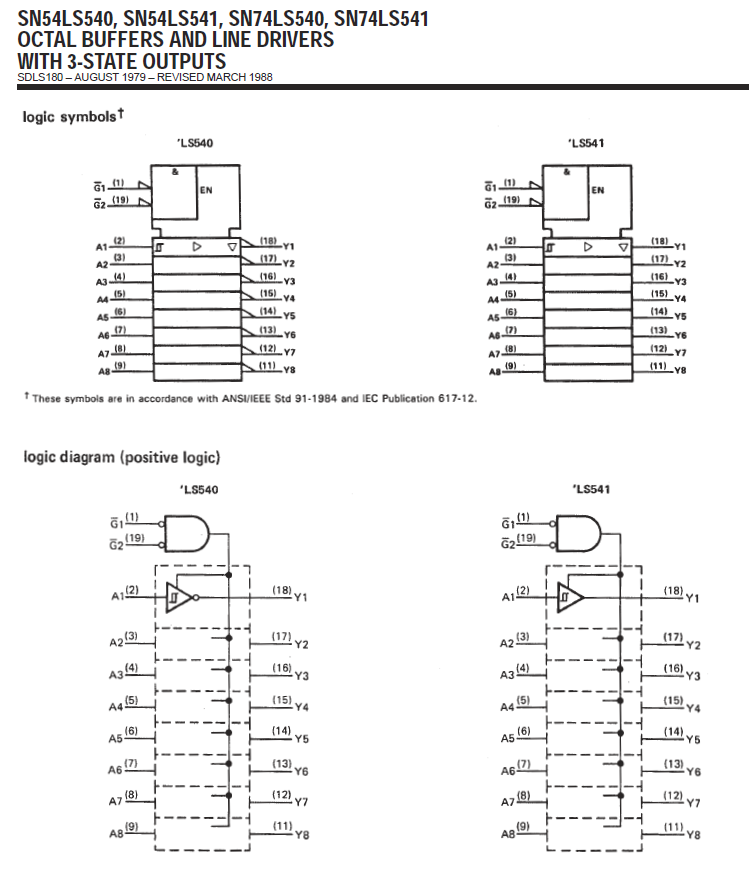

pour la suite je viens de m'apercevoir que la simulation du 74LS540 est fausse ( il se comporte comme un 74LS541 et n'inverse pas les sorties )

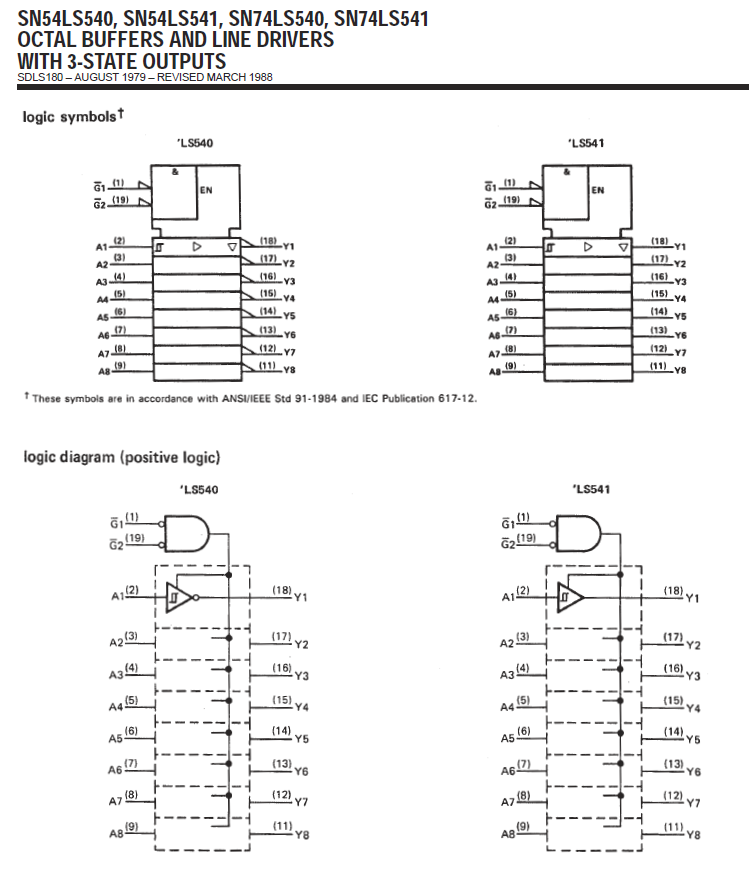

voici le DATASHEET de ces 2 composant on y voit bien que dans le LS540 les sorties sont inversées

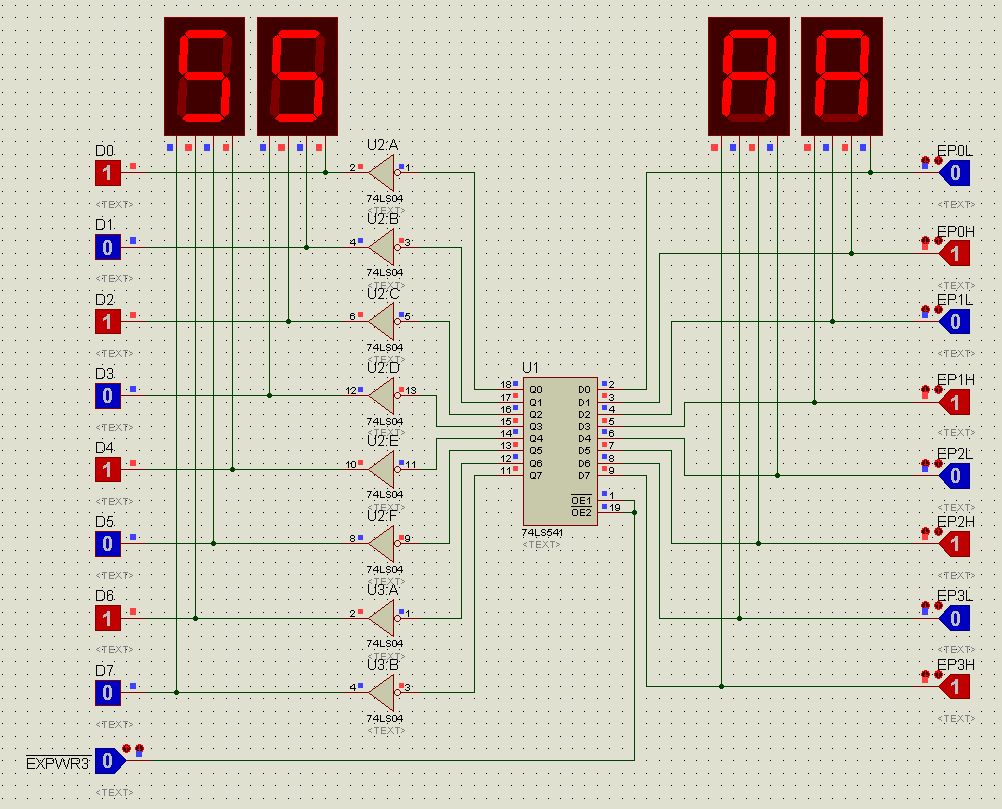

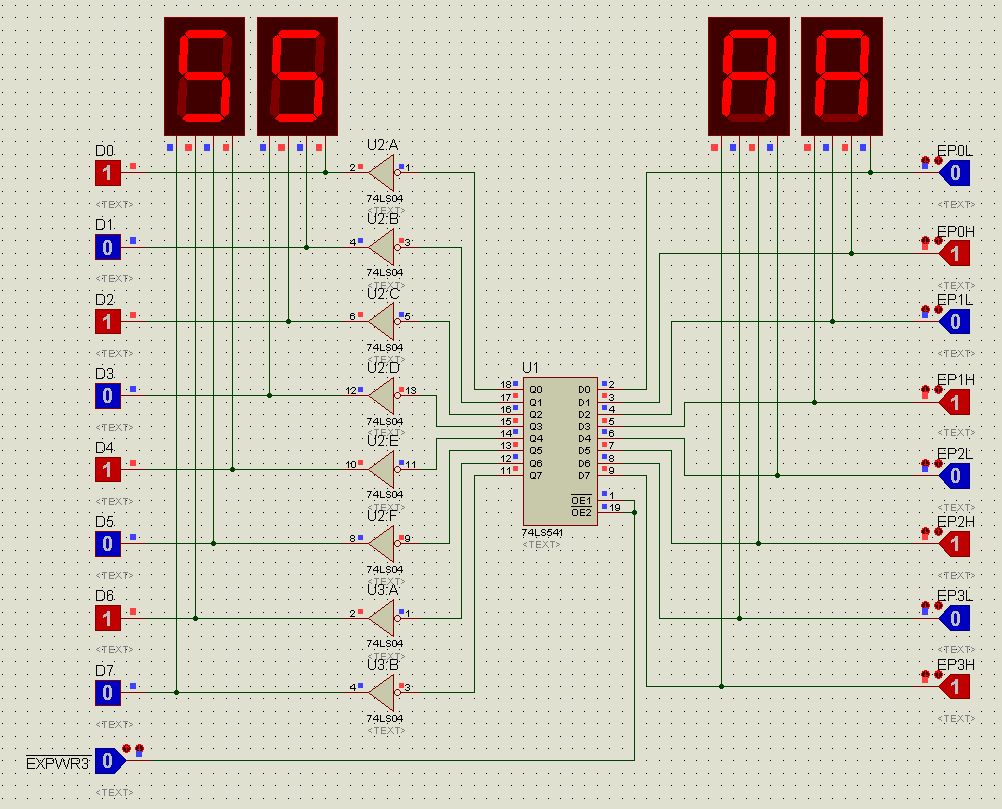

j'ai donc fait un schéma avec des LS04 pour inverser le signal a la sortie du LS541 ce qui donne un LS540

et voici comment les valeurs se retrouvent inversées a la lecture a l'adresse FFFFh ( exemple pour un Philips 8250 )

voici le DATASHEET de ces 2 composant on y voit bien que dans le LS540 les sorties sont inversées

j'ai donc fait un schéma avec des LS04 pour inverser le signal a la sortie du LS541 ce qui donne un LS540

et voici comment les valeurs se retrouvent inversées a la lecture a l'adresse FFFFh ( exemple pour un Philips 8250 )

voir ci-dessus

"voici le décodage des portes qui gérent les signaux /SLTSL /RD et /WR

il faut savoir qu'un signal noté / est actif au niveau bas ( 0V )

en mode écriture"

Donc si je comprend bien

les signaux "pur" ex D0 à D7 , A0 .... sont a la "VCC"

les signaux surligné ex /WR /RD /SLTSL sont eux a la GND

??? je pensait le contraire !!

"voici le décodage des portes qui gérent les signaux /SLTSL /RD et /WR

il faut savoir qu'un signal noté / est actif au niveau bas ( 0V )

en mode écriture"

Donc si je comprend bien

les signaux "pur" ex D0 à D7 , A0 .... sont a la "VCC"

les signaux surligné ex /WR /RD /SLTSL sont eux a la GND

??? je pensait le contraire !!

TURBO-R FS-A1ST 512/128ko MSX2+ NMS 8250 F4 /Fix Audio /Ram 1/4Mb VDP9958 VRAM 192ko 2FDD SANYO WAVY PHC35J MSX2 NMS 8280 Ram 4Mb VDP9938 VRAM 192ko 2FDD NMS 8250 128/128ko 2FDD VG8235/39 128/128ko 1FDD SONY HB-F700D MSX1 MC810 32/16k VG 8020 64k HB75F 64k HX-22 64k RS232/ CX5M 32k HB501F EXT : My Exp 4X/[b] MegaFlashSCC 512ko/BERT R2/BEER CF/SUNRISE 2CF/FUNRICE V2.01/MAXIOL/MEGASCSI HDD-CD/SDMSX 1SD/FMPAC SRAM/NMS1205+1160/RS 232 Harukaze/GR8NET/DOS2/ HOMER V2 RAM512ko/Floppy Pack/MAXduino/ROM1664/FM Pak /GR8NET /AMIGA/ PC/ RaspB Pi(B) / ARDUINO

voici en images pourquoi les pokes &HFFFF sont différents suivants les MSX qui ont un slot expander en interne

en fait ça dépend dans quel slot est située la mémoire et le fameux poke met les bank de mémoire dans le même slot

dans l'ordre

en fait ça dépend dans quel slot est située la mémoire et le fameux poke met les bank de mémoire dans le même slot

dans l'ordre

SONY HB700 poke&hFFFF,&HFF ou 255 SLOT 3.3

PHILIPS 8250 poke&hFFFF,&HAA ou 170 SLOT 3.2

TURBO-R poke&hFFFF,&H0 ou 0 SLOT 3.0

PHILIPS 8250 poke&hFFFF,&HAA ou 170 SLOT 3.2

TURBO-R poke&hFFFF,&H0 ou 0 SLOT 3.0

Donc si je comprend bien

les signaux "pur" ex D0 à D7 , A0 .... sont a la "VCC"

les signaux surligné ex /WR /RD /SLTSL sont eux a la GND

les signaux "pur" ex D0 à D7 , A0 .... sont a la "VCC"

les signaux surligné ex /WR /RD /SLTSL sont eux a la GND

tous ces signaux passent de l'état 0 a l'état 1 en permanence , aucun n'est figé au +5v ou au GND

ils sont actifs a l'état 1 pour une notation normale

ils sont actifs a l'état 0 pour une notation avec /

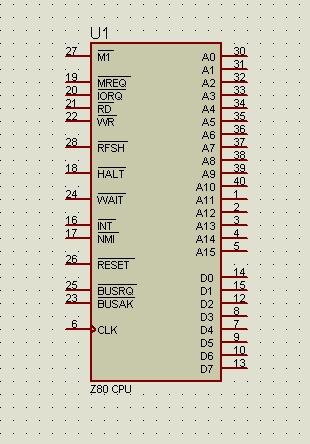

voici les signaux d'un Z80

ceux avec un trait par dessus que je remplace par / dans du texte ça veut dire signaux inverses donc actifs a l'état 0

la sélection des pages de 16K elle se fait par les Bits d'adresses A14 et A15, c'est similaire a la mémoire vue par le Z80

une page de 16k a 14 bits de 0 a 13, pour calculer c'est 2^14 = 16384

une page de 16k a 14 bits de 0 a 13, pour calculer c'est 2^14 = 16384

Répondre

Vous n'êtes pas autorisé à écrire dans cette catégorie