L'école Changer DRAM par SRAM interne 8250

Reprise du message précédent

Jipe :

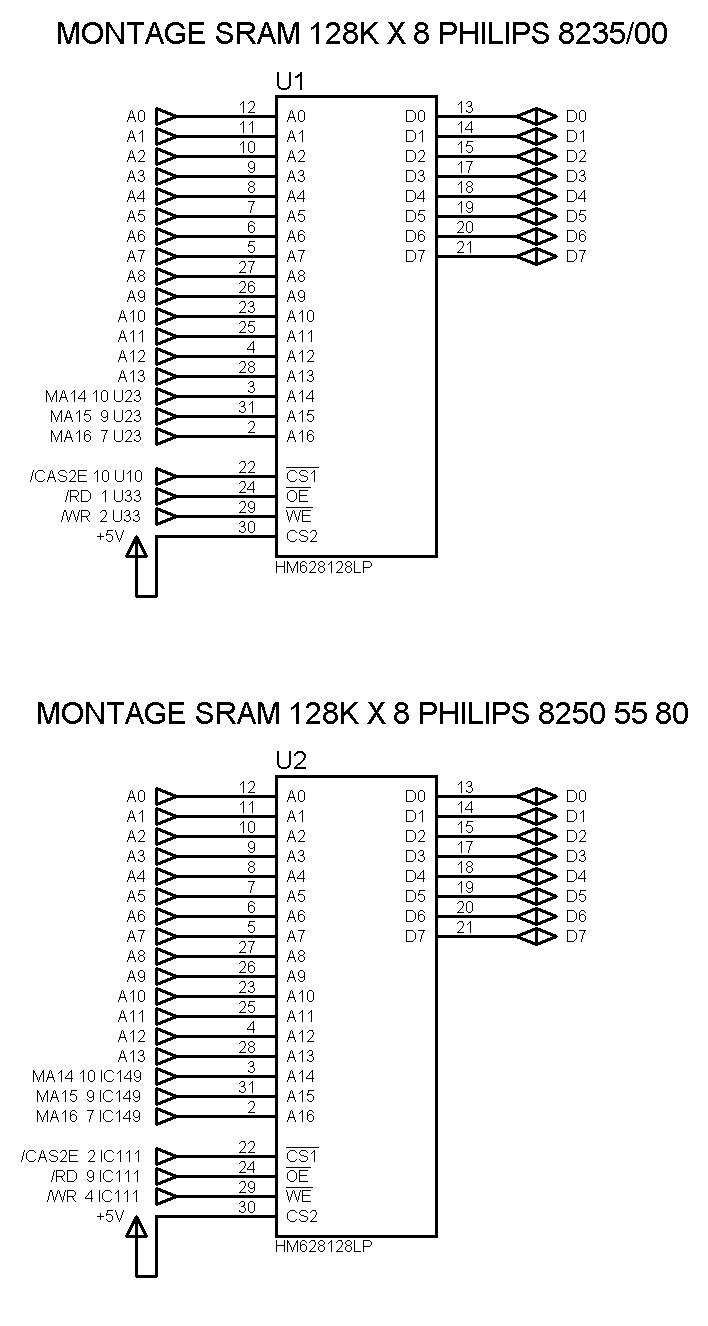

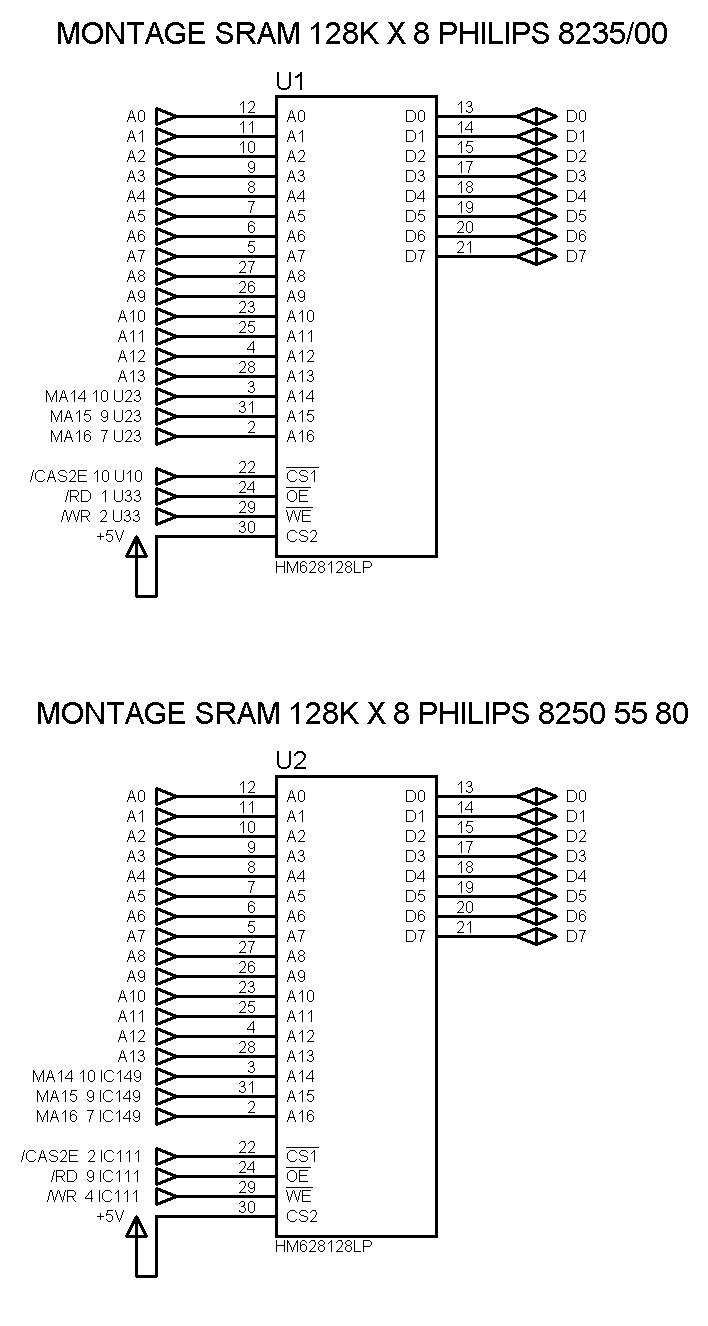

Je n'ai retrouvé pas retrouvé la carte mère mais seulement les notes du montage et fait le schéma pour le 8235/00 et les 8250 55 et 80

bien sur les 2 x 74LS157 du multiplexage ne servent plus a rien dans ce cas

bien sur les 2 x 74LS157 du multiplexage ne servent plus a rien dans ce cas

Est-ce que ceci est aussi possible pour le Video RAM?

on en parle ici avec un schéma et tu y as posté

https://www.msx.org/forum/msx-talk/hardware/v9938-compatible-sram?page=1

https://www.msx.org/forum/msx-talk/hardware/v9938-compatible-sram?page=1

Jipe :

on en parle ici avec un schéma et tu y as posté

https://www.msx.org/forum/msx-talk/hardware/v9938-compatible-sram?page=1

https://www.msx.org/forum/msx-talk/hardware/v9938-compatible-sram?page=1

J'ai lu cette pdf:

https://cdn.hackaday.io/files/1608516881849184/SRAM%20Replacement%20for%20TMS99x8%20VRAM.pdf

Circuit sur page 7

Je ne comprends tout simplement pas l'inversion du signal RW en WR puis de WR en RD. Quel signal est lequel ? Qu'est-ce qui vient du VDP et que se passe-t-il sur quelle connexion de la SRAM. Le VDP9938 possède CAS0 et CAS1, doivent-ils être combinés avec une porte AND?

le PDF dont tu parle est pour un VDP de MSX1

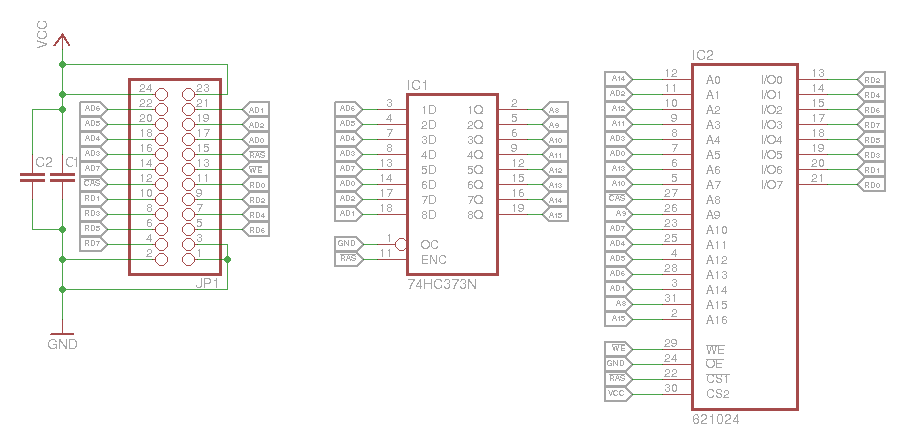

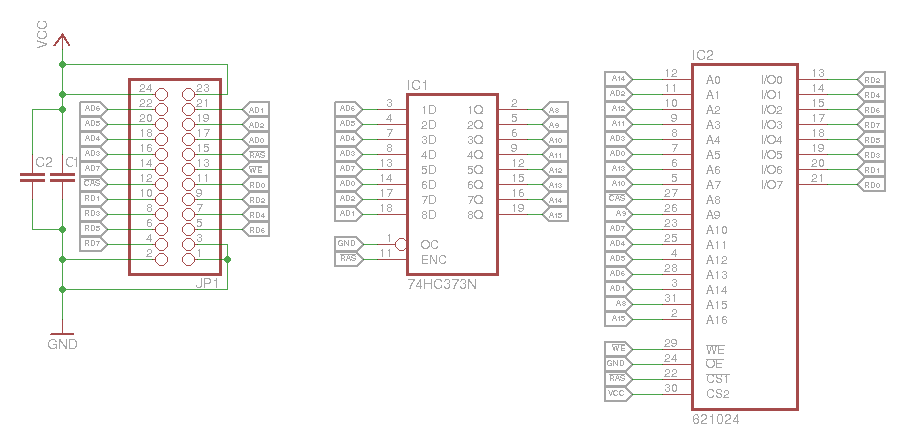

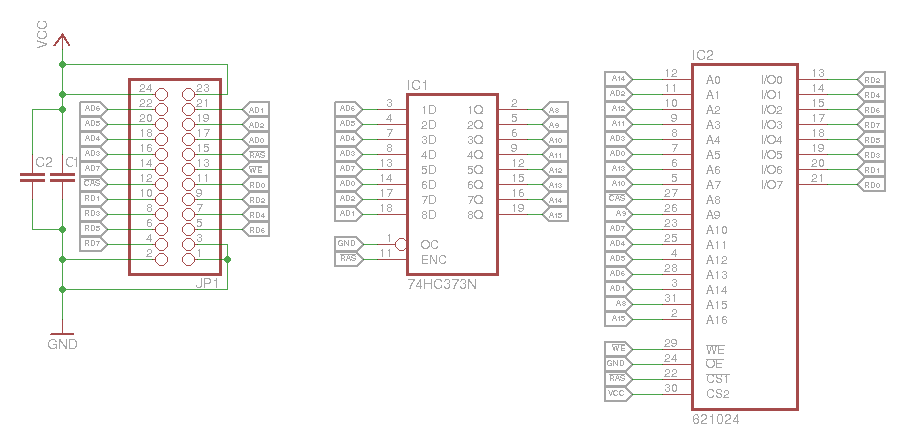

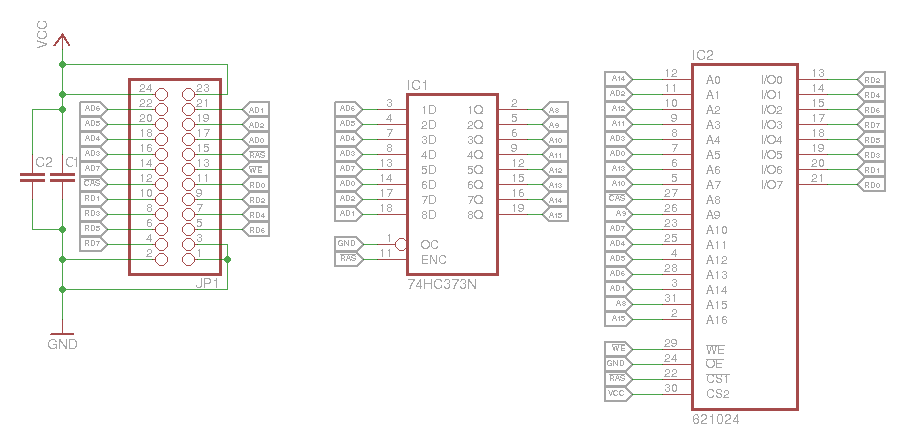

c'est le schéma d'avant de msxegor qui est pour le V9938

je l'ai retravaillé un peu pour qu'il soit plus lisible au niveau des pins

ce schéma est à l'origine pour un CX5MII d'où le connecteur JP1

il faut le remplacer par les signaux pris sur les 2 vrams

les numérotations de la sortie du HC373 ne correspondent pas à celles des signaux de la SRAM

il faut juste relier la pin A15 du HC373 au A15 qui est en fait le A16 de la SRAM par exemple

je peux te faire le schéma pour aller dans un 8250 si ce n'est pas clair pour toi

attention je n'ai jamais tenté ce montage et dans la suite du post on parle de SRAM à 70ns mais qu'il vaut mieux utiliser des 55ns

c'est le schéma d'avant de msxegor qui est pour le V9938

je l'ai retravaillé un peu pour qu'il soit plus lisible au niveau des pins

ce schéma est à l'origine pour un CX5MII d'où le connecteur JP1

il faut le remplacer par les signaux pris sur les 2 vrams

les numérotations de la sortie du HC373 ne correspondent pas à celles des signaux de la SRAM

il faut juste relier la pin A15 du HC373 au A15 qui est en fait le A16 de la SRAM par exemple

je peux te faire le schéma pour aller dans un 8250 si ce n'est pas clair pour toi

attention je n'ai jamais tenté ce montage et dans la suite du post on parle de SRAM à 70ns mais qu'il vaut mieux utiliser des 55ns

Oke merci Jipe, si je comprend bien on en prend aucun signal du VDP?

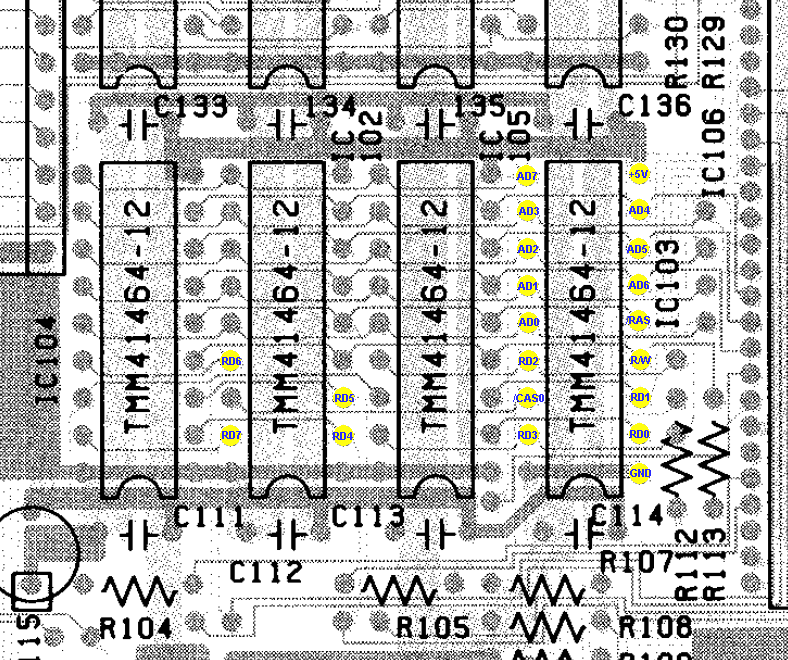

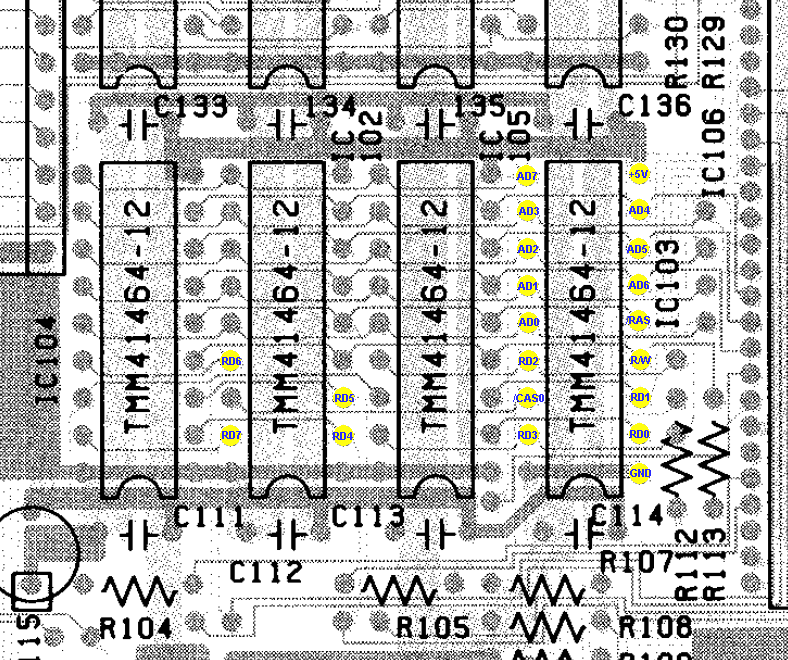

Il y a 4 puces pour le VRAM. lesquels dois-je prendre? IC102 et IC105?

Je pense que c'est clair pour commencer le modif. Edité par Gregory Le 28/01/2025 à 01h30

Il y a 4 puces pour le VRAM. lesquels dois-je prendre? IC102 et IC105?

Je pense que c'est clair pour commencer le modif. Edité par Gregory Le 28/01/2025 à 01h30

Jipe :

voici ou prendre les signaux met des supports pour pouvoir revenir en arrière au cas ou

R/W c'est /WE

R/W c'est /WE

Tu connais un fast 55ns 128Kx8 SRAM?

J'ai trouvé ceci: AS6C1008-55SIN Edité par Gregory Le 30/01/2025 à 23h51

Jipe :

le PDF dont tu parle est pour un VDP de MSX1

c'est le schéma d'avant de msxegor qui est pour le V9938

je l'ai retravaillé un peu pour qu'il soit plus lisible au niveau des pins

ce schéma est à l'origine pour un CX5MII d'où le connecteur JP1

il faut le remplacer par les signaux pris sur les 2 vrams

les numérotations de la sortie du HC373 ne correspondent pas à celles des signaux de la SRAM

il faut juste relier la pin A15 du HC373 au A15 qui est en fait le A16 de la SRAM par exemple

je peux te faire le schéma pour aller dans un 8250 si ce n'est pas clair pour toi

attention je n'ai jamais tenté ce montage et dans la suite du post on parle de SRAM à 70ns mais qu'il vaut mieux utiliser des

55ns

c'est le schéma d'avant de msxegor qui est pour le V9938

je l'ai retravaillé un peu pour qu'il soit plus lisible au niveau des pins

ce schéma est à l'origine pour un CX5MII d'où le connecteur JP1

il faut le remplacer par les signaux pris sur les 2 vrams

les numérotations de la sortie du HC373 ne correspondent pas à celles des signaux de la SRAM

il faut juste relier la pin A15 du HC373 au A15 qui est en fait le A16 de la SRAM par exemple

je peux te faire le schéma pour aller dans un 8250 si ce n'est pas clair pour toi

attention je n'ai jamais tenté ce montage et dans la suite du post on parle de SRAM à 70ns mais qu'il vaut mieux utiliser des

55ns

Quelle est la raison de l'envoi du signal CAS à la broche 27 (A8) de la SRAM ?

https://www.msx.org/forum/msx-talk/hardware/v9938-compatible-sram?page=1

indiqué par " @mohai : "

- Cas sur A8 est normal :

sur puce SRAM il faut décoder un espace RAM de 128Ko et en conception DRAM vous avez 2 bancs de 64Ko .

La sélection entre chaque 64 Ko avec CAS dans la conception DRAM peut être comprise dans la conception SRAM comme un décodage d’adresse haute entre la partie haute et basse de l’espace d’adressage de 128 Ko.

Ce serait plus clair si Cas était sur A16, mais sur A8, cela fonctionne aussi, peut-être simplement plus facile à router sur un PCB simple face.

Vous pouvez utiliser soit CAS0, soit CAS1, peu importe, CASX ne doit pas être utilisé.

- ras sur CS fonctionnera car il reste basse pendant les 2 cycles, même le second.

- pour le databus, je suppose que le signal /WR sur la sram dépasse le /OE low pour la direction

du bus de données, donc /WE low + /OE low fait le bus d’entrée/S de la sram

...

je viens de vérifier 621024 fiche technique c’est comme ça :

si /WE est faible alors peu importe la valeur sur /OE le bus de données est entré pour la sram et il va

alors permettre à vdp de définir sa valeur à écrire . Edité par bpmsx Le 01/02/2025 à 09h24

indiqué par " @mohai : "

- Cas sur A8 est normal :

sur puce SRAM il faut décoder un espace RAM de 128Ko et en conception DRAM vous avez 2 bancs de 64Ko .

La sélection entre chaque 64 Ko avec CAS dans la conception DRAM peut être comprise dans la conception SRAM comme un décodage d’adresse haute entre la partie haute et basse de l’espace d’adressage de 128 Ko.

Ce serait plus clair si Cas était sur A16, mais sur A8, cela fonctionne aussi, peut-être simplement plus facile à router sur un PCB simple face.

Vous pouvez utiliser soit CAS0, soit CAS1, peu importe, CASX ne doit pas être utilisé.

- ras sur CS fonctionnera car il reste basse pendant les 2 cycles, même le second.

- pour le databus, je suppose que le signal /WR sur la sram dépasse le /OE low pour la direction

du bus de données, donc /WE low + /OE low fait le bus d’entrée/S de la sram

...

je viens de vérifier 621024 fiche technique c’est comme ça :

si /WE est faible alors peu importe la valeur sur /OE le bus de données est entré pour la sram et il va

alors permettre à vdp de définir sa valeur à écrire . Edité par bpmsx Le 01/02/2025 à 09h24

bpmsx

Répondre

Vous n'êtes pas autorisé à écrire dans cette catégorie