# LES OSCILLATEURS: DU "RC" AU QUARTZ

Le quartz est devenu, dans l'esprit du public, synonyme de haute précision pour la mesure du temps.

A propos, qu'est-ce qu'un quartz ? Pour le physico-chimiste, c'est la forme cristalline de l'oxyde de silicium. Eh oui, encore du silicium : décidément, la panacée de l'électronique contemporaine!

### L'anneau instable

Nous le savons bien depuis que nous avons décrit les bistables set/reset et autres bascules D, un anneau composé d'un nombre pair d'inverseurs est une mémoire, c'est-à-dire un système qui se maintient dans un état stable.

En revanche, un anneau composé d'un nombre **impair** d'inverseurs est par essence **instable**. Son comportement est une course sans fin vers un équilibre impossible: « 0 en entrée, donc 1 en sortie, donc 1 en entrée, donc... »

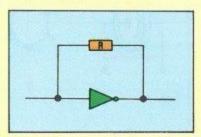

La vitesse à laquelle un anneau comme celui de la figure 1 passe d'un état à l'autre est déterminée par le retard que l'on introduit entre la sortie de l'inverseur et son entrée. L'anneau est fugitivement en équilibre, tant que l'élément de retard n'a pas été « traversé ».

### Des délais cumulés

La figure 1 est bien trop théorique pour que nous sachions construire des oscillateurs qui marchent réellement. En revanche, c'est un bon « guide de pensée », pour l'analyse des oscillateurs présents dans les montages ; on recherchera systématiquement la fonction inverseuse (un véritable inverseur, un ampli-opérationnel...) et la fonction de délai.

Ainsi, la figure 2 présente, redessiné, un oscillateur dont nous avons déjà usé et abusé, où l'on reconnaît :

l'inverseur du type « à hystérésis »,

la cellule RC comme élément de retard.

Fig. 1. – Principe général des oscillateurs tout-ou-rien: un anneau avec un nombre impair d'inverseurs (ici: 1) assorti d'éléments de retard.

Fig. 2. – Interprétation de l'oscillateur RC avec inverseur à hystérésis ; le RC s'identifie au « retard ».

En fait, une analyse vraiment complète doit tenir compte des **retards** internes à l'inverseur (qui ne commute jamais instantanément), et aussi de ses traits singuliers, comme dans notre cas le trigger de Schmitt qui déplace les seuils de la commutation.

### Un diapason de cristal...

Les montages « RC » sont bien intéressants, ne serait-ce que parce qu'ils ne coûtent pas cher. Aussi conviennent-ils partout où l'on n'a que des exigences de précision limitées (klaxon, clignoteur...).

Lorsque l'on veut atteindre à une précision helvète, force est de trouver autre chose, car les montages RC les plus soignés ne peuvent guère donner mieux que 1 %, et avec des composants courants, c'est plutôt 5 %... Sans parler des variations avec la température!

La clé de l'horlogerie moderne, c'est le fameux quartz devenu si populaire dans nos montres et réveils. Cela, tout le monde le sait.

Ce que l'on sait moins, c'est que l'« inventeur » du quartz est le même Pierre Curie (avec Jacques Curie) qui s'est par ailleurs rendu célèbre dans l'aventure de la radioactivité.

C'est à partir de ses travaux que l'on a pu utiliser des cristaux comme de véritables diapasons... ultra sensibles à l'électricité.

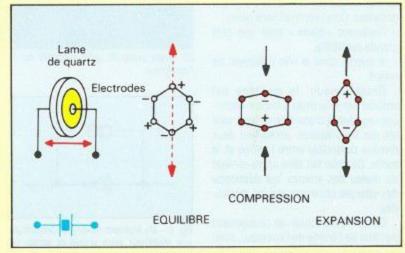

Fig. 3. — Principe des « quartz ». Les déformations de la lame de cristal produisent des flux de charges électriques, et vice-versa. Il y a une résonance pour un ( ultra-) « son » qui dépend de la taille de la lame.

### ... piézo-électrique

Un cristal de quartz, c'est un édifice composé d'atomes de silicium et d'atomes d'oxygène, selon un motif de base hexagonal. En fait, c'est un peu plus compliqué qu'à la **figure 3**, mais celleci nous suffira pour imaginer ce qui se passe dans une mince lame de quartz sur laquelle sont fixées deux électrodes.

Le cristal est taillé de telle sorte que les « centres de charge électrique » (marqués + et – sur la figure) sont alignés à la perpendiculaire des électrodes

Quand le réseau subit une compression, un déséquilibre se crée qui « charge » les deux faces du cristal ; il en est de même s'il subit une expan-

Un quartz : ce composant n'a pas de sens défini.

sion. En bref, si l'on tape sur le cristal dans la bonne direction, il se comporte comme un générateur.

Réciproquement, si l'on applique sur les électrodes des oscillations électriques, le quartz va vibrer. Il s'agit d'un phénomène mécanique et, comme pour une cloche ou un diapason, il y a une fréquence de résonance qui dépend de la taille du cristal.

Avec et sans jeu de mots!

### Pour exciter le quartz

Les modèles physiques et mathématiques du quartz vibrant sont plutôt complexes, d'autant que le cristal n'est pas seul en cause; citons: le montage des électrodes, la capacité du boîtier qui va le protéger...

Il en résulte non une seule, mais deux fréquences de résonance dites « série » et « parallèle » ; au demeurant, très voisines.

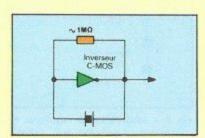

Les montages classiques pour exciter le quartz, c'est-à-dire pour le faire vibrer à fréquence de résonance, font pour la plupart intervenir des inverseurs biaisés (biased) comme à la figure 4. La résistance R ad hoc dépend de la technologie : un million d'ohms est une valeur courante pour des com-

MICRO-SYSTEMES - 117

posants C.MOS, quelques centaines d'ohms pour des portes TTL.

L'effet peut s'imaginer intuitivement. La résistance est juste assez faible pour apporter une certaine contribution aux changements d'état (elle « relève le 0 » et « abaisse le 1 »), mais pas trop faible pour aller jusqu'à l'instabilité dont il a été question tout à l'heure.

### L'anneau C.MOS

La figure 5 est sans doute le schéma du plus simple des oscillateurs à quartz possibles. On y reconnaît sans peine :

- l'inverseur « biaisé » pour une plus grande sensibilité,

- le quartz, dans le rôle d'élément de retard.

Grosso modo, le montage est amorcé par le premier « choc » électrique reçu par le cristal quand l'inverseur est mis sous tension, présentant deux niveaux contrastés entre l'entrée et la sortie. Ce choc fait faire un va-et-vient au réseau des atomes, qui développe des charges contraires sur les électrodes.

Ce qui va provoquer un changement de l'état de l'entrée de l'inverseur, donc de sa sortie, donc nouveau choc inverse, etc. Le quartz « sonne »... à une fréquence qui peut atteindre couramment le million de fois par seconde (MHz).

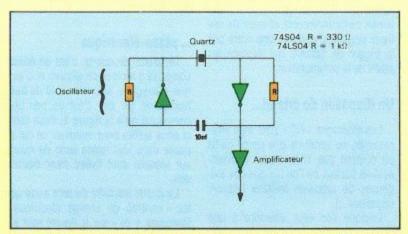

La figure 6 indique un autre montage très, très classique, qui se réalise cette fois avec des inverseurs TTL. Son fonctionnement est un petit peu plus compliqué à décrire, mais il a l'avantage de supporter des rapidités dix fois supérieures. L'auteur l'a utilisé sans problèmes de 1 MHz à 4 MHz avec des inverseurs 74LS04; on préférera des composants plus rapides (74S04) pour aller jusqu'à 12 MHz environ.

### Une mise en forme

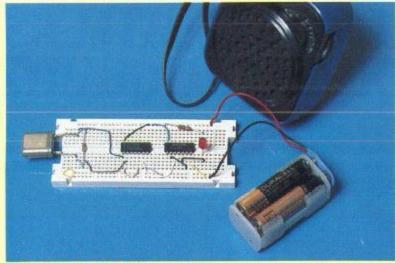

Notre montage pratique complétera ce (trop) bref aperçu de la question des horloges à quartz en introduisant, parderrière l'oscillateur proprement dit, deux « étages » de nature à fournir un signal bien meilleur que celui présent dans l'anneau proprement dit.

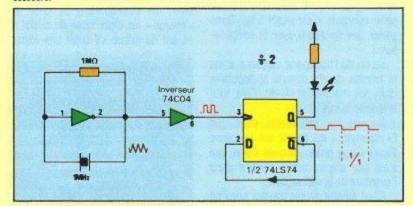

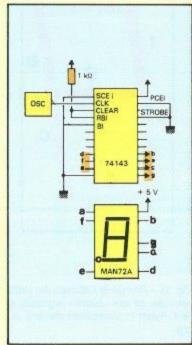

Cet anneau sera monté avec un inverseur C.MOS courant : l'une des portes d'un 74C04 (fig. 7). Elle est biaisée par une résistance de 1 MΩ, et reliée aux deux « pattes » d'un quartz de 1 MHz environ(\*). Les quartz n'ont bien entendu pas de sens défini ; le seul conseil pratique, c'est de ne pas les faire tomber ou leur taper dessus : ils sont parfois vulnérables aux chocs.

Le premier élément de mise en

Un simple poste de radio commuté sur P.O. permet de vérifier le bon fonctionnement de l'oscillateur.

Fig. 4. — Un inverseur rendu plus sensible par une résistance entre entrée et sortie. Les électroniciens parlent « d'amener l'ampli dans sa région de fonctionnement finéaire ».

Fig. 5. – Le plus simple des oscillateurs à quartz : un inverseur C.MOS avec 1  $M\Omega$  environ en retour, et le quartz dans la boucle.

Fig. 6. – Montage très classique (et virtuellement înratable) avec des inverseurs TTL qui couvre les applications de 1 MHz à plus de 10 MHz : gamme des horloges usuelles pour les microprocesseurs.

Fig. 7. – Montage d'expérience. On « recevra » les deux fréquences sur un poste de radio (sur 300 et 600 m environ, en PO). On court-circuite le quartz pour rendre les changements audibles, et visibles par le témoin LED.

forme est un second inverseur, emprunté au même circuit intégré. Outre sa fonction de relais, cet inverseur va donner une allure plus « carrée » au signal qui circule dans l'oscillateur. Ceux qui ont vu ce genre de signal sur un oscilloscope reconnaîtront qu'il fait davantage penser à des hautes herbes qu'à des créneaux de château-fort!

### Soigner le rapport cyclique

Un autre inconvénient du signal d'horloge « brut » est habituellement sa dissymétrie. Il y a des applications où l'on se moque de la durée relative des temps « haut » et « bas » de l'horloge. Dans d'autres, non.

Nous avons vu dans les Fiches nº 7 un artifice tout à fait convenable pour obtenir un signal rigoureusement symétrique à partir d'une horloge qui ne l'est pas : on la divise par deux (en fréquence) grâce à une bascule D travaillant sur flanc, et rebouclée sur sa sortie complémentaire.

Le principe est très sain. Pour obtenir une horloge bien propre de fréquence F, on prendra un quartz taillé pour 2 F, que l'on montera comme à la figure 5 ou 6. Une division par deux donnera l'horloge désirée.

### Avec un poste de radio

Il n'est pas nécessaire de disposer d'un oscilloscope pour vérifier que le montage marche bien. Il suffit d'avoir à côté de la planchette un poste de radio ordinaire, commuté sur la gamme des petites ondes (marquée PO ou MW).

En effet, l'oscillateur va se comporter comme un petit émetteur sur la fréquence 1 MHz, c'est-à-dire sur une longueur d'onde voisine de 300 mètres.

Dès que l'on a réglé le poste sur la bonne « station », l'effet est le suivant ; le bruit de fond du récepteur s'atténue lorsque l'oscillateur est en marche, et réapparaît si on le bloque (il suffit de court-circuiter les pattes de quartz).

On retrouve le même phénomène, mais plus net, en réglant sur 500 kHz (voisinage de 600 mètres). C'est normal, le courant délivré par le diviseur par deux est bien plus fort que celui des C.MOS; donc l'« émetteur » est plus puissant!

Une LED témoin visualise également le fonctionnement : elle brille plus fort si on bloque l'oscillateur, moins si on le laisse fonctionner ; auquel cas la diode reçoit moitié moins de courant.

(\*) On trouve dans le commerce deux valeurs très voisines : 1 MHz ou 1,024 MHz, qui nous conviennent aussi bien.

## DES COMPTEURS

Au suivant.... Au suivant... (\*\*).

Le poète a chanté ainsi la plus monotone des opérations arithmétiques : le comptage.

Derrière chaque horloge de l'univers micro-informatique, il y a un compteur qui, tel l'adjudant de la chanson, détermine l'opération suivante. A moins qu'il ne serve à mesurer le temps qui passe...

### L'addition binaire

Rien de plus simple que l'addition binaire, c'est-à-dire avec deux chiffres seulement.

0 + 0 = 0; ce n'est pas difficile.

0 + 1 = 1; pas trop dur non plus,

1 + 1 = 0... et l'on retient 1; vraiment, c'est très élémentaire!

C'est avec ces règles que débute toute l'« arithmétique binaire » des ordinateurs, celle qui est matérialisée par les montages logiques. En bref, celle qui nous intéresse ici.

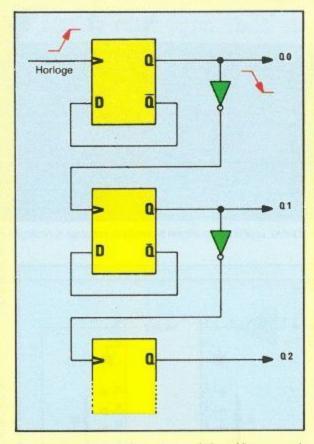

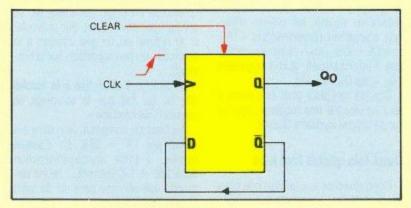

La figure 8 donne, avec la bascule D travaillant sur flanc que nous avons décrite dans les Fiches nº 7, le plus simple des compteurs binaires que l'on se peut concevoir. La simple recopie de la « valeur contraire » (Q) fait bien passer la sortie Q de 0 à 1 puis de 1 à 0 et ainsi de suite, au rythme de l'horloge (CLK).

### Plus d'un chiffre

Pour compter avec plus d'un chiffre, il va falloir donner un sens (électronique) à la retenue. Retenue que l'on appelle aussi le report (carry en langue

Examinons le tableau d'un comptage binaire sur, disons, trois chiffres:

(0) 0 0 0 (1) 0 0 1 (2) 0 1 0 +1 (2)

0 1 12 1 0 02 (4)

12 (5) 1 0

1 1 04 (6)11

Fig. 9. - Un montage qui compte sur plusieurs bits par reports en cascade. Chaque changement de 1 à 0 fait changer le bit suivant,

00 0 Q1

Fig. 10. - Un compteur synchrone à deux bits. Le OU-exclusif « prédit » la valeur suivante du bit Q1, en fonction des valeurs courantes de Qo et Q1.

Il est clair que la règle des reports est celle-ci : si un chiffre passe de 1 à 0, alors le chiffre suivant, celui qui est présenté à gauche selon notre coutume, doit changer. Ainsi, on passe en binaire de cinq à six de façon mécani-

- le chiffre le plus à droite (unité) change, de 1 à 0; - on fait donc, selon cette règle, chan-

ger le suivant de 0 en 1;

le chiffre le plus à gauche ne change

CLEAR

#### La retenue baladeuse

Avec des bascules D et des inverseurs, il est aisé de matérialiser cette méthode de comptage (fig. 9). Les bascules successives ont leurs sorties baptisées Qo, Q1, Q2... pour dénoter leurs poids binaires croissants.

Ces bascules, par exemple autant de moitiés de 74LS74, ont leur sortie complémentaire rebouclée sur l'entrée D. de telle sorte qu'elles changent d'état sur chaque flanc ascendant d'horloge. Avec un inverseur intercalé, notre cahier des charges sera complètement respecté: si Qo passe de 1 à 0, le flanc

ad hoc arrive sur la bascule suivante, et Q1 change, etc.

Le lecteur avisé dira que l'inverseur est inutile, qu'il suffit de relier le « Q » de chaque bascule à l'entrée d'horloge de la suivante. Correct!

Le montage fonctionne de proche en proche: s'il y a retenue sur un certain chiffre, cela fait changer le suivant. Puis, si ce chiffre donne une retenue, on fait changer le suivant...

Pour les électroniciens anglophones, c'est la « retenue baladeuse » (ripple

### Le compteur synchronisé

Les compteurs à retenue baladeuse fonctionnent, mais avec un phénomène qui n'est pas toujours indifférent : la retenue se propage de proche en proche, de telle sorte qu'il y a un délai entre le changement du premier chiffre,

Fig. 8. - Le compteur binaire le plus rudimentaire, à un chiffre : la recopie de l'état contraire dans la bascule D, à chaque « top » d'horloge, fait l'affaire. On peut essayer avec un 74LS74.

celui du suivant, etc., jusqu'au dernier.

Si le compteur a beaucoup de chiffres, ces retards qui se totalisent peuvent devenir une gêne vis-à-vis d'exigences de rapidité.

L'alternative, c'est le compteur synchrone (synchronous counter). C'est-à-dire un montage où tous les chiffres en même temps vont prendre leur valeur suivante.

La figure 10 en est un exemple très simplifié, puisqu'elle met en œuvre un compteur à deux bits seulement. Le tableau de comptage montre que le « prochain Q<sub>1</sub> » sera 1 si Q<sub>0</sub> et Q<sub>1</sub> sont différents, sinon 0. Le changement de Q<sub>0</sub> s'effectue comme précèdemment ; tandis que le changement de Q<sub>1</sub> a lieu au même instant (l'horloge arrive en parallèle sur les deux bascules), par recopie d'un OU-exclusif entre « ancien Q<sub>0</sub> et ancien Q<sub>1</sub> ».

La recette est très simple : on demande à un montage logique auxiliaire de **prédire la prochaine valeur** des différents chiffres. La rapidité n'est plus limitée que par ce montage logique... Dans cette limite, on peut affirmer que tous les chiffres du comptage changent ensemble.

### Un compteur intégré

Dans les catalogues de circuits intégrés, la famille des compteurs est importante : compteurs binaires, décimaux, synchronisés ou non...

Cette variété correspond à des besoins fort différents et pour la plupart justifiés. D'ordinaire, les livres d'électronique digitale font grand cas de cette « zoologie » des compteurs, car leur utilité est très grande, diverse et variée, notamment dans les instruments de mesure.

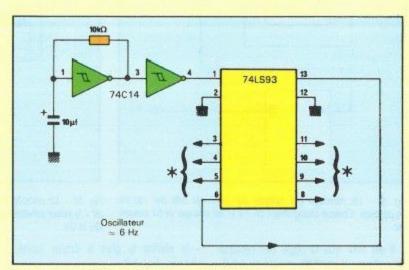

Pour l'informaticien, l'individu le plus représentatif est (en technologie TTL) le circuit 74LS393, dont le schéma-bloc est donné à la figure 11.

C'est un double compteur, qui

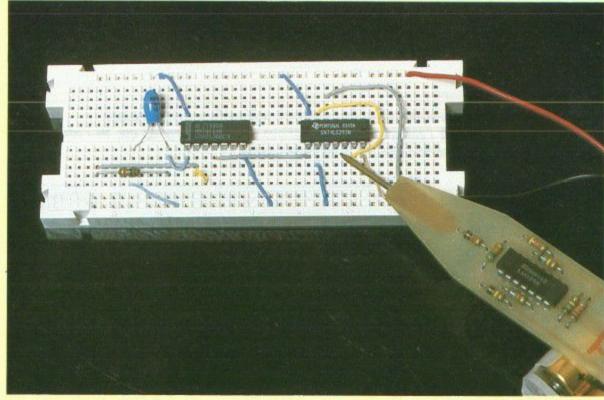

Ce montage oscille environ à 6 Hz. Le pèse signaux permet le contrôle du comptage de l'horloge sur les différentes broches du 74393.

Fig. 12. – Le 74LS393 devient un compteur à 8 bits si l'on connecte le plus fort des bits d'un premier compteur, à l'entrée d'horloge du suivant. On vérifie que les rythmes aux sorties successives sont des divisions par deux de la fréquence de l'oscillateur : 6 Hz environ.

10A 2CLEAR

10A 2CLEAR

10C 208

10C 200

Fig. 11. – Vue détaillée du double compteur à quatre bits 74LS393. Le flanc de comptage actif (haut vers bas) n'est pas spécifié au hasard, mais de telle sorte que joue la règle des reports pour les compteurs en cascade (ce qui est le cas).

contient deux blocs identiques de comptage sur 4 bits. Dans la nomenclature en vigueur, les entrées d'horloge s'appellent respectivement « 1A » et « 2A ». Les « Q<sub>A</sub> » sont les sorties que l'informaticien aurait appelées « Q<sub>0</sub> », les Q<sub>B</sub> : Q<sub>1</sub>, etc.

Chaque compteur peut être remis à zéro en bloc par une impulsion positive sur sa broche auxiliaire CLEAR.

### Deux fois quatre font huit

Contrairement aux latches que nous avons déjà vus, c'est cette fois le flanc qui est actif pour déclencher le comptage proprement dit. Ce choix n'est pas arbitraire, comme nous allons le voir grâce à notre montage d'expérience de la figure 12.

En effet, ce flanc actif est le bon choix si l'on veut respecter la « règle des reports » que nous avons énoncée tout à l'heure. Il suffit de connecter une sortie d'un compteur à l'entrée d'horloge d'un autre pour qu'ils se retrouvent (arithmétiquement) mis bout à bout.

Notre 74LS393 est attaqué par l'oscillateur favori de l'auteur, bouclé sur un 74C14. Avec les valeurs indiquées, il bat à peu près à la cadence de 6 fois par seconde.

Les entrées de remise à zéro sont mises à la masse pour que le circuit tourne en « pur » comptage ; sa valeur de début importe peu pour notre propos.

Sur la broche 3, il est aisé avec le pèse-signaux de vérifier le comptage binaire de l'horloge, autrement dit, sa division par deux (3 Hz). Sur la broche 4, le rythme est un peu inférieur à la seconde; un peu supérieur, sur la broche 5.

La broche 6 est reliée à la broche 13; ce qui fait que le comptage se poursuit « en cascade ».

Au bout du compteur, le rythme est divisé par 28 = 256. En d'autres termes, le cycle allumage/extinction dure 256 x 1/6 seconde... ce qui demande une certaine patience au saint Thomas que vous êtes!

(\*\*) Jacques Brel

## **UN STANDARD COMPLEXE:**

### COMPTEUR DECIMAL+LATCH+AFFICHEUR A 7 SEGMENTS

Dans la fiche précédente, on évoquait la « zoologie » des compteurs intégrés : pas moins de quarante références dans un catalogue

Les individus les plus complexes combinent en un seul bloc un compteur, une mémoire et un dispositif d'affichage... en clair!

### Compter en décimal

A proprement parler, les circuits logiques ne comptent jamais en décimal, seulement en binaire.

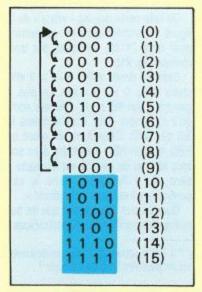

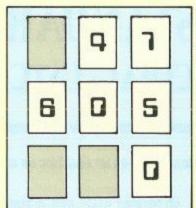

Certains dispositifs comptent en B.C.D. (binary coded decimal), c'est-àdire que sur les seize combinaisons possibles de 4 bits, on ne garde que les dix premières (fig. 13).

Fig. 13. - Le code « décimal codé binaire » ou DCB; on ne se sert que des dix premières combinaisons de 4 bits, pour représenter les chiffres de 0 à 9.

Un compteur B.C.D., c'est en pratique un compteur binaire semblable à celui de notre Fiche 9B, à ceci près qu'on le « truque » avec une logique qui force le retour à zéro après la combinaison 1001.

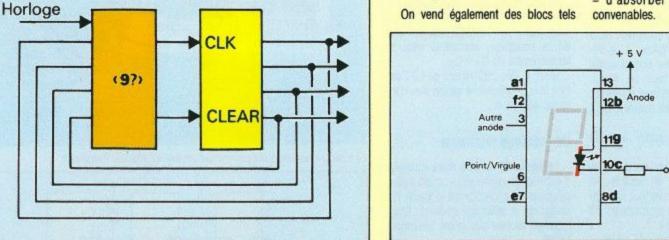

Le principe général est donné à la figure 14. Si votre curiosité est piquée, ouvrez les catalogues...

A propos, pourquoi diable s'échiner à compter par dizaines ? Comptez vos doigts, et accumulez plusieurs millénaires d'habitudes... vous avez la réponse.

### L'affichage à sept-segments

Du score des matches de football aux tableaux de bord des avions, en passant par les pendules numériques, l'affichage de chiffres décimaux est omniprésent dans notre vie quotidienne.

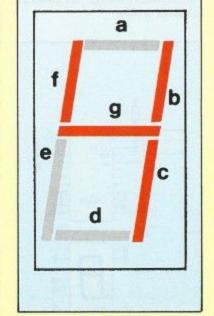

Un des procédés les plus simples pour faire apparaître ces chiffres, consiste à allumer/éteindre des « seqments » disposés comme à la figure 15.

Il existe une nomenclature « universelle » de ces sept bâtonnets, on dit : 7-segments; elle part de a pour la barre supérieure. On tourne ensuite jusqu'à f dans le sens des aiguilles

Fig. 15. - Principe de l'affichage des chiffres décimaux sur sept « bâtons » (segments). Ici, le 4. Retenir la nomenclature standard, de a

d'une montre ; le segment milieu vient en dernier, c'est a.

On réalise ce schéma de nombreuses façons : panneaux géants à mouvement électromagnétique, cristaux liquides des montres...

### Affichage à LEDs

On vend également des blocs tels

que celui de la figure 16 (afficheur MAN72A); ils sont conditionnés comme des circuits intégrés : largeur, écartement entre broches...

Noyés dans ce bloc, il y a autant de diodes LED que de segments; plus une, qui permet d'illuminer un « point » utile lorsque l'on a une... virgule. Il faut nous faire à cette idée : les Anglo-Saxons utilisent le point dans les nombres, là où nous mettons une virgule. Mais c'est leur technologie qui est dominante, et notre virgule a de bonnes chances de tomber en désuétude... faute de composants (\*\*\*)!

A partir d'un point commun référencé Anode, ces LEDs sont reliées à autant de broches nommées comme à la figure 15; de telle sorte qu'un montage ad hoc peut illuminer sélectivement les différents segments; et « composer » les différents chiffres.

Les précautions sont celles des LEDs au détail; pas d'excès de tension/courant.

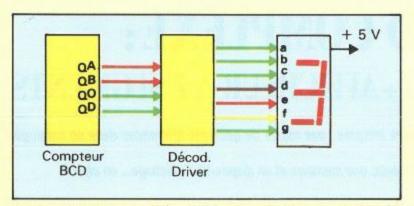

### Un compteur lisible

L'ensemble d'un compteur et d'un tel afficheur forme un compteur « lisible ». Encore faut-il faire intervenir un nouvel organe, que l'on appelle decoder-driver, qui a pour mission (fig. 17): - de convertir le code B.C.D. en consignes d'allumage de tel et tel segment,

- d'absorber les tension/courant convenables.

Fig. 16. - Un bloc luminescent comme le MAN72A comporte 7 + 1 LEDs « noyées » dans les segments. Electriquement, ce ne sont que de simples LEDs connectées à un point-source commun (Anode), toutes indépendantes par ailleurs.

Fig. 14. - Un compteur décimal. De 0 à 9, c'est un simple compteur binaire ; la logique ad hoc (\* 9 ? \*) provoque après 9 une remise à zéro par CLEAR, au lieu d'une progression par CLK.

Fig. 17. – Un décodeur/driver traduit le code BCD en commandes d'allumage : des niveaux bas avec appel de courant par des collecteurs ouverts, s'agissant de LEDs.

Fig. 18. – Le 74143, circuit intégré complexe comportant en chaîne: un compteur BCD, un latch, un décodeur/driver.

Sur l'exemple où le compteur BCD affiche trois en binaire, le décodeur affiche des « 0 » sur les lignes a, b, c, d et g pour provoquer les appels de courant qui donnent forme au « 3 ».

### Un standard pas simple : le 74143

Le circuit intégré à 24 broches 74143 est pour l'essentiel un compteur BCD associé sur la même « puce » à un décodeur pour LEDs. Plus une quantité de gadgets qui ont tous un sens... parce que l'affichage décimal s'adresse aux humains, et que les humains sont compliqués!

Son brochage est donné à la figure 18.

Nous n'aurons pas la place, dans ces colonnes, de décrire en totalité les fonctions du 74143. Le lecteur est renvoyé aux manuels des fournisseurs s'il veut vraiment tout savoir.

Nous nous contenterons de localiser, hors les alimentations qui sont aux extrémités habituelles, trois groupes de lignes, coloriées sur la figure :

Fig. 19. – Le montage le plus simple du 74143 : comptage et affichage « transparent » des dix chiffres.

le compteur proprement dit est attaqué par l'horloge CLK, on se doute de ce que signifie CLEAR; le reste est moins simple, citons MAX COUNT, qui est une sorte de report conditionnel;

« derrière » le compteur BCD, un latch activé par STROBE recopie l'état de ce compteur, accessible sous sa forme binaire via Q<sub>A</sub> à Q<sub>D</sub>;

enfin, le décodeur/pilote de LED délivre le code affichable via (on s'en douterait) les a, b, c...

### Un montage minimum

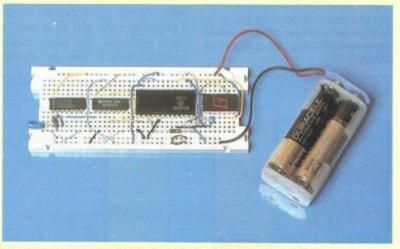

La figure 19 montre notre montage d'expérience « minimum », c'est-à-dire, remplissant la fonction de la figure 17 : comptage + affichage décimal; l'horloge est fournie par notre oscillateur favori.

Un certain nombre de points sont reliés à la masse ou à une « source de 1 ». Les sorties de commande de LED

Fig. 20. – Illustration de ce qui est considéré comme un affichage « normal » avec suppression des zéros à gauche.

sont connectées aux points de même nom de l'afficheur.

Sauf erreur de câblage, ça doit « tourner », comptez de 0 à 9 et ainsi de suite.

Une bonne façon de comprendre les diverses entrées d'option consiste à les changer... et observer les différences. Commençons par enlever la liaison de STROBE vers la masse : le compteur se « fige » en l'état. Cette commande prend tout son sens dans les appareils où l'on compte des événements (ou le temps) jusqu'à ce que tel ou tel critère d'arrèt soit rencontré.

Par exemple, un chronométrage de course commencera par une mise à zéro (CLEAR au pistolet du starter), et se terminera en « gelant » le compte de temps (mettez STROBE à 0 toute la course, et basculez à 1 au passage de la ligne). Il n'y a plus qu'à lire le résultat

### Les zéros à gauche

Rétablissons STROBE, et relions RBI (Ripple Blanking Input) à la masse au lieu du « 1 ».

Tout fonctionne comme avant, du moins en ce qui concerne les chiffres de 1 à 9 ; en revanche, au lieu d'afficher 0, le bloc à LEDs s'éteint!

Voilà un exemple (parmi d'autres) de l'élément humain.

Ecrivez-vous Marignan 0001515 ? Si oui, on a déjà dû vous regarder d'un drôle d'air !

Nous considérons tout naturel, si un compteur à plusieurs chiffres nous est présenté, que les fameux « zéros à gauche » soient ... éteints (fig. 20). Sauf, peut-être, celui qui est « le plus à droite ».

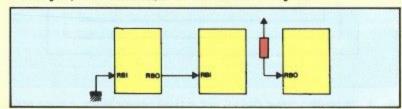

L'entrée RBI, au niveau bas, signifie « éteignez le zéro ». Une sortie RBO signifie « je suis éteint parce que je contiens zéro » (actif au niveau bas).

De telle sorte que les « effets » de la figure 20 s'obtiennent en connectant ainsi trois 74143, solidaires des trois chiffres (fig. 21).

Celui de droite a RBI à « 1 ». Il affichera donc 0 s'il y a lieu. Le plus à gauche a son RBI à « 0 », de telle sorte qu'il s'éteindra pour 0 et signalera le fait par RBO. Celui du milieu reçoit ce RBO sur son RBI; il éteindra donc son zéro si celui de gauche est lui-même à zéro, ou l'illuminera dans le cas contraire, s'il est bien « significatif ».

Quand nous vous disons que les humains ne simplifient pas l'électronique!

(\*\*\*) Les amateurs de normes protectionnistes ont peut-être une idée à creuser ?

Le montage expérimental d'un compteur décimal sur afficheur 7 segments.

Fig. 21. – Usage des broches de fonction BRI et BRO pour donner le résultat de la figure 20.

## POUR CEUX QUI VEULENT ALLER PLUS LOIN

### L'horloge à deux phases

Grāce à un diviseur par deux, par exemple une simple bascule D travaillant sur flanc, nous avons su égaliser le rapport cyclique; autrement dit, les temps « haut » et « bas » de l'horloge sont égaux.

Une autre propriété de ce genre de montage, c'est qu'il délivre deux signaux d'horloge de polarité opposée; dans une nomenclature traditionnelle, on peut les baptiser respectivement 0<sub>1</sub> et O<sub>2</sub>.

Si l'on considère le flanc « actif » de tels signaux, faisant référence (par exemple) aux bascules D, on voit bien que l'on dispose alternativement d'un flanc actif sur O<sub>1</sub>, puis sur O<sub>2</sub>, etc. Avec, entre ces flancs, un intervalle d'une demi-période de l'horloge.

C'est grâce à des horloges de ce genre que les réseaux logiques que nous avons dessinés dans notre précédent numéro vont prendre toute leur puissance...

### Le P.L.A. bien tempéré

Nos Fiches nº 8 concluaient sur le caractère « universel » de montages ET/OU arrangés en lignes et colonnes régulières. On prouve en effet sans trop de difficulté que toutes les expressions de la logique peuvent être évaluées par de tels réseaux programmables (P.L.A.

= Programmable Logic Array).

Hélas! Hélas!

Dans l'électronique logique réelle,

### La valse du P.L.A.

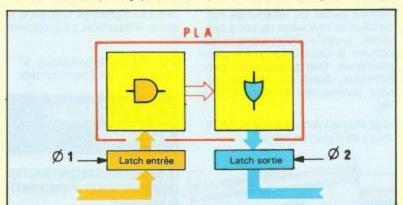

Un P.L.A. devient un bloc logique très civilisé si on le munit (fig. A) de deux registres *latches* en entrée et en sortie, charun actionné par l'une des deux horloges en question.

Sur la **première phase** (0<sub>1</sub>), les « données » sont recopiées dans le latch d'entrée où elles sont stabilisées jusqu'au même flanc de cette horloge.

Le P.L.A. passe ensuite par une période d'instabilité: plus précisément, les signaux doivent « traverser » les divers composants internes avant que le « résultat » se stabilise à la sortie du tableau-OU.

C'est alors qu'interviendra 0<sub>2</sub>, pour recopier ce résultat dans le latch de sortie où il restera stable jusqu'à la fin du prochain cycle. 0<sub>2</sub> donne la deuxième phase.

En résumé, la valse du P.L.A. bien synchronisé a ses temps :

(1) sur 0<sub>1</sub>, recopie des entrées dans un latch;

(2) temps de décision, c'est-à-dire, traversée du P.L.A.;

(3) recopie du résultat dans un latch de sortie.

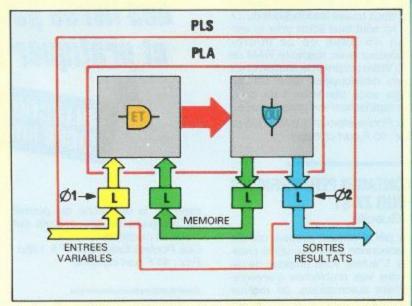

### Du P.L.A. à l'automate P.L.S.

Par surcroît, 01 et 02 définissent, pour le reste du montage, des instants

Fig. A. – Le P.L.A. entre un registre d'entrée et un registre de sortie actionnés par les deux phases d'horloge. La période instable (décision) est encadrée par ces deux phases. Des instants sains pour changer les entrées ou exploiter les sorties sont précisément définis.

aucun système de portes ET/OU ne travaille instantanément. Pire encore, un réseau logique dont les entrées varient « trop vite » peut faire, au sens commun, n'importe quoi...

En revanche, si les entrées sont stables un certain temps, un P.L.A. donne après le délai nécessaire le résultat attendu. ou I'on peut :

faire varier les entrées sans inconvénient (flanc montant de 0<sub>2</sub>),

exploiter des sorties stables (flanc de 0<sub>1</sub>).

Cette rigueur dans la spécification des « bons moments » est très appréciable dans les logiques complexes. Ne vous y trompez pas, lecteurs.

Fig. B. – Une partie des entrées/sorties sert de « mémoire » au P.L.A.; le tout devient un « séquenceur programmable » ou P.L.S. C'est l'élément de base des unités centrales (microprocesseurs, circuits d'interface complexes...). On trouve aussi des composants P.L.S., chez Texas et Signetics notamment.

### C'EST COMME CELA QUE FONCTIONNENT LES MICROPROCESSEURS!

Pour ceux qui dessinent ces fabuleux circuits intégrés que sont les microprocesseurs et leurs blocs d'interface complexes, les « briques » du jeu de construction sont :

des registres et mémoires interconnectés par des « chemins » plus ou moins multiplexés,

des blocs de décision ayant peu ou prou le schéma de la figure B.

Ainsi monté, le P.L.A. devient P.L.S. (Programmable Logic Sequencer).

### Le P.L.S.: un P.L.A. qui sait où il en est

La figure B est en fait une simple variante de la figure A. On a simplement « bouclé » quelques lignes du latch de sortie... sur le latch d'entrée.

L'effet de ce bouclage est de réaliser une machine « intelligente » rudimentaire ; pour les théoriciens, un automate de Mealy.

Où est la soi-disant intelligence ?

Elle réside justement dans la « mémoire » du dispositif, ces quelques bits d'information dont dispose le réseau logique pour « savoir », d'un cycle d'horloge à l'autre, « où il en est ».

A chaque cycle, voici (intuitivement) ce qui se passe: le réseau prend simultanément un certain nombre de décisions du genre « je suis dans cet état (mémoire), il se passe ceci sur les entrées (variables), alors je modifie les sorties en conséquence (résultats) et je note que je suis dans tel nouvel état (mémoire) ».

### De bonnes lectures

Si le lecteur n'a jamais fait un programme, on conçoit que cet énoncé soit obscur. En revanche, s'il a déjà programmé, en Basic, en langage machine ou en n'importe quoi, il aura reconnu un processus habituel: en fonction de l'état des lieux (où on est dans le programme) et tenant compte de tel ou tel événement (test), on décide de faire telle ou telle chose, et d'orienter la suite du programme dans telle ou telle direction.

Le P.L.S. est tout juste plus puissant que cela, car certaines décisions/actions peuvent être prises en même temps, alors que les programmes ne font jamais qu'une chose à la fois...

Le lecteur **vraiment** vraiment curieux peut lire à ce sujet le merveilleux ouvrage de référence de Carver Mead et Lynn Conway: *Introduction to VLSI* systems Addison-Wesley 1980 (\*\*\*\*).

C'est un livre difficile, mais pas inabordable pour ceux qui nous ont suivis jusqu'ici dans notre série d'initiation. On y apprend, entre autres, que les circuits à très haute intégration se réussissent précisément grâce à des schémas réguliers du genre P.L.A./ P.L.S...

Bon, bon courage!

(\*\*\*\*) Existe en version française depuis peu.